# phyCORE®-AM57x

## **Hardware Manual**

Document No.: L-815e\_3

SOM Prod. No.: **PCM-057** SOM PCB. No.: **1428.3**

CB Prod. No.: **PCM-948** CB PCB. No.: **1435.2**

Edition: March 2018

In this manual are descriptions for copyrighted products that are not explicitly indicated as such. The absence of the trademark ( $^{\text{TM}}$ ) and copyright ( $^{\text{CM}}$ ) symbols does not imply that a product is not protected. Additionally, registered patents and trademarks are similarly not expressly indicated in this manual.

The information in this document has been carefully checked and is believed to be entirely reliable. However, PHYTEC America LLC assumes no responsibility for any inaccuracies. PHYTEC America LLC neither gives any guarantee nor accepts any liability whatsoever for consequential damages resulting from the use of this manual or its associated product. PHYTEC America LLC reserves the right to alter the information contained herein without prior notification and accepts no responsibility for any damages which might result.

Additionally, PHYTEC America LLC offers no guarantee nor accepts any liability for damages arising from the improper usage or improper installation of the hardware or software. PHYTEC America LLC further reserves the right to alter the layout and/or design of the hardware without prior notification and accepts no liability for doing so.

© Copyright 2018 PHYTEC America LLC, Bainbridge Island, WA.

Rights - including those of translation, reprint, broadcast, photomechanical or similar reproduction and storage or processing in computer systems, in whole or in part - are reserved. No reproduction may occur without the express written consent from PHYTEC America LLC.

## **Table of Contents**

| Tab  | le of Co | ntents                              | 3  |

|------|----------|-------------------------------------|----|

| List | of Figu  | res                                 | 6  |

| List | of Tabl  | es                                  | 7  |

| Cor  | vention  | ns, Abbreviations and Acronyms      | 9  |

| Pre  | face     |                                     | 11 |

| Par  | t I: PCM | -057/phyCORE-AM57x System on Module | 13 |

| 1    | Intr     | oduction                            | 14 |

|      | 1.1      | Block Diagram                       | 16 |

|      | 1.2      | Component Placement Diagram         | 17 |

| 2    | Pin      | Description                         | 19 |

| 3    | Pov      | ver                                 | 29 |

|      | 3.1      | 5.0V System Power (VCC_5V0_IN)      | 29 |

|      | 3.2      | 3.3V System Power (VCC_3V3_IN)      | 29 |

|      | 3.3      | 3.3V SD Power (VDD_SD)              | 29 |

|      | 3.4      | Off-chip RTC Power (VBAT)           | 30 |

|      | 3.5      | Power Management IC (U3)            | 30 |

| 4    | Rea      | I-Time Clock (RTC)                  | 32 |

|      | 4.1      | AM57x RTC                           | 32 |

|      | 4.2      | External RTC                        | 32 |

| 5    | Syst     | tem Configuration and Booting       | 33 |

|      | 5.1      | GPMC Configuration for XIP/NAND     | 33 |

|      | 5.2      | QSPI Redundant SBL Images Offset    | 34 |

|      | 5.3      | Boot Device Order                   | 34 |

|      | 5.4      | Boot Peripheral Pin Multiplexing    | 35 |

| 6    | Syst     | tem Memory                          | 36 |

|      | 6.1      | DDR3 SDRAM (U8, U9, U10, U11, U12)  | 36 |

|      | 6.2      | eMMC Memory (U5)                    | 37 |

|      | 6.3      | NAND Flash Memory (U14)             | 37 |

|      | 6.4      | I <sup>2</sup> C EEPROM (U18)       | 38 |

|      | 6.5      | QSPI NOR Flash Memory (U7)          | 38 |

|      | 6.6      | Memory Model                        | 38 |

| 7    | SD/      | MMC Card Interfaces                 | 39 |

| 8    | Seri     | al Interfaces                       | 40 |

|      | 8.1      | USB                                 | 40 |

|      |          |                                     |    |

| 8.2         | Ethernet                                             | 40 |

|-------------|------------------------------------------------------|----|

| 8.3         | I <sup>2</sup> C                                     | 41 |

| 8.4         | SATA                                                 | 41 |

| 8.5         | PCIe                                                 | 41 |

| 9 De        | ebug Interface                                       | 42 |

| 10          | Technical Specifications                             | 43 |

| 11          | Hints for Integrating and Handling the phyCORE-AM57x | 45 |

| 11.1        | Integrating the phyCORE-AM57x                        | 45 |

| 11.2        | Handling the phyCORE-AM57x                           | 45 |

| Part II: PC | M-948/phyCORE-AM57x Carrier Board                    | 46 |

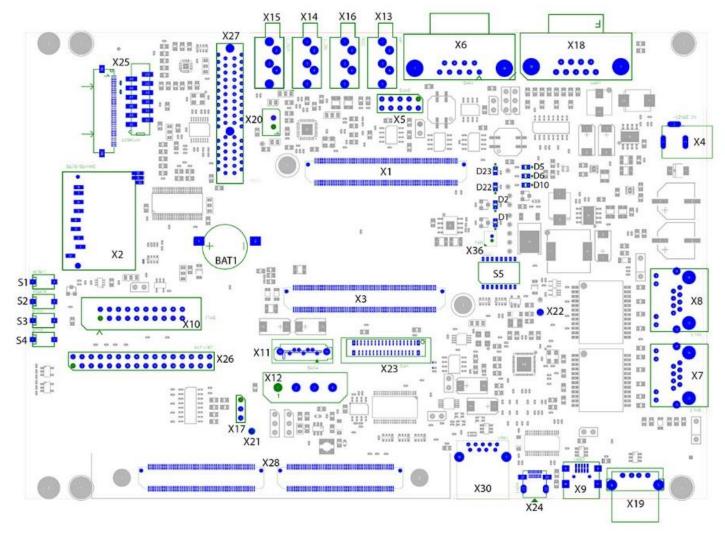

| 12          | Introduction                                         | 47 |

| 13          | Overview of Peripherals                              | 48 |

| 13.1        | Connectors and Headers                               | 48 |

| 13.2        | Buttons and Switches                                 | 49 |

| 13.3        | LEDs                                                 | 49 |

| 14          | Jumpers                                              | 51 |

| 15          | phyCORE-AM57x SOM Connectivity                       | 54 |

| 16          | Power                                                | 55 |

| 16.1        | 5V Supply                                            | 56 |

| 16.2        | 3V3 Supply                                           | 57 |

| 16.3        | 1V8 Supply                                           | 57 |

| 16.4        | Battery                                              | 57 |

| 16.5        | Current Measurement                                  | 57 |

| 17          | Controller Area Network (CAN)                        | 58 |

| 17.1        | CAN1                                                 | 58 |

| 17.2        | CAN2                                                 | 59 |

| 18          | SDIO/SD/MMC                                          | 60 |

| 19          | WiFi/Bluetooth Connector                             | 61 |

| 20          | Ethernet                                             | 63 |

| 20.1        | ETH0                                                 | 63 |

| 20.2        | ETH1                                                 | 63 |

| 21          | USB                                                  | 65 |

| 21.1        | USB1                                                 | 65 |

| 21.2        | USB2                                                 | 66 |

| 22          | RS-232                                               | 67 |

| 23        | SATA                             | 70  |

|-----------|----------------------------------|-----|

| 24        | JTAG                             | 72  |

| 25        | PCIe                             | 74  |

| 26        | Display                          | 76  |

| 26        | 5.1 HDMI                         | 76  |

| 26        | 5.2 LVDS                         | 77  |

| 27        | Touch Controller                 | 79  |

| 28        | Camera                           | 80  |

| 29        | Audio                            | 81  |

| 30        | Cooling Fan Connector            | 83  |

| 31        | User Buttons                     | 84  |

| 32        | User LEDs                        | 85  |

| 33        | Boot Mode Selection              | 86  |

| 34        | System Reset Button              | 88  |

| 35        | GPIO Expansion Connector         | 89  |

| Part III: | : PCM-957 GPIO Expansion Board   | 90  |

| 36        | Introduction                     | 91  |

| 37        | Power Signal Mapping             | 92  |

| 38        | Control and Reset Signal Mapping | 93  |

| 39        | GPMC Signal Mapping              | 94  |

| 40        | GPIO Signal Mapping              | 95  |

| 41        | VIN3A (Display) Signal Mapping   | 96  |

| 42        | SPI Signal Mapping               | 97  |

| 43        | I <sup>2</sup> C Signal Mapping  | 98  |

| 44        | QSPI1 Signal Mapping             | 99  |

| 45        | KBD Signal Mapping               | 100 |

| 46        | PWM/Clock/Wakeup Signal Mapping  | 101 |

| Revisio   | on History                       | 102 |

## **List of Figures**

| Figure 1. phyCORE-AM57x Block Diagram                                                      | 16 |

|--------------------------------------------------------------------------------------------|----|

| Figure 2. phyCORE-AM57x Component Placement (top view)                                     |    |

| Figure 3. phyCORE-AM57x Component Placement (bottom view)                                  | 18 |

| Figure 4. Pinout of the phyCORE-Connector (top view, with cross section insert)            | 20 |

| Figure 5. Power Supply Diagram                                                             | 30 |

| Figure 6. phyCORE-AM57x Mechanical Dimensions (top down view as seen from controller side) | 43 |

| Figure 7. phyCORE-AM57x Carrier Board                                                      |    |

| Figure 8. Overview of Peripherals                                                          | 48 |

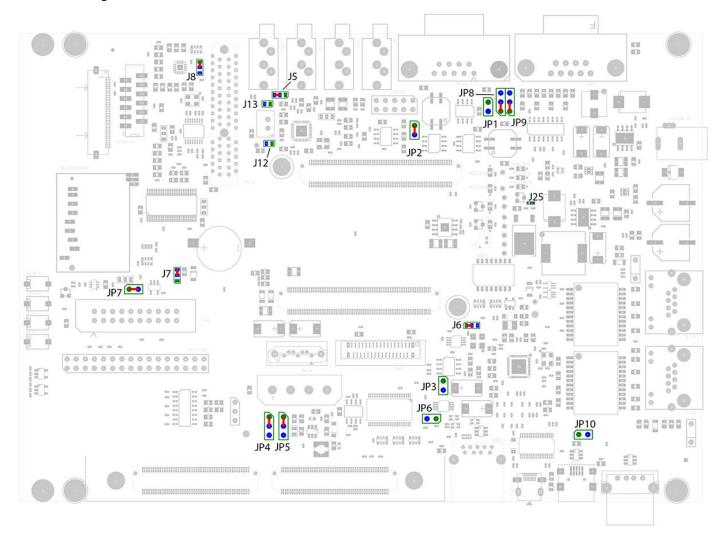

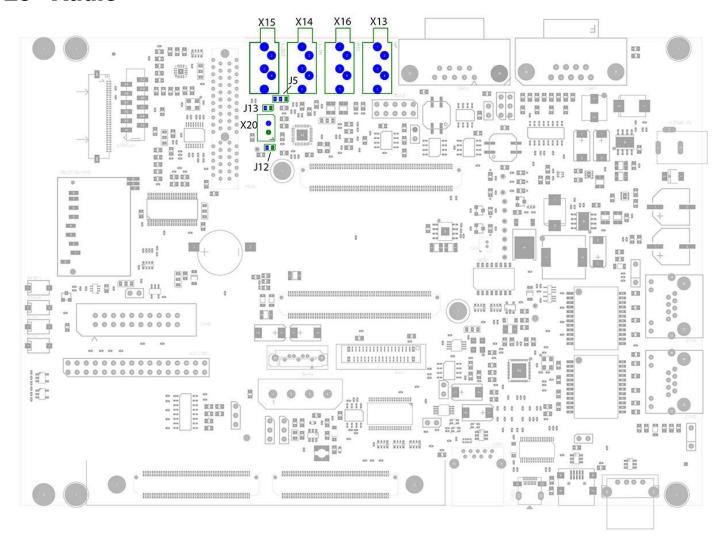

| Figure 9. Jumper Locations and Default Settings                                            | 51 |

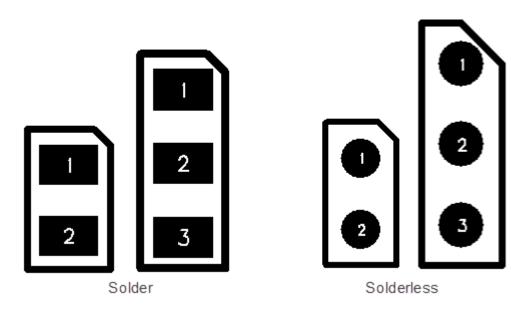

| Figure 10. Jumper Numbering Scheme                                                         | 52 |

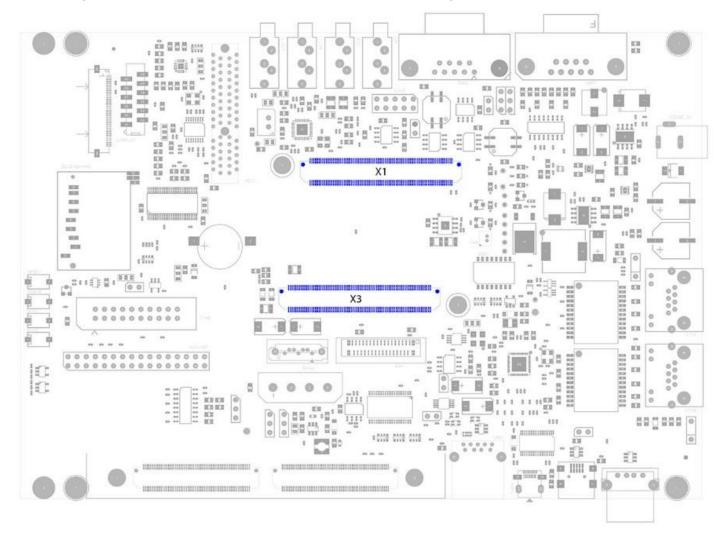

| Figure 11. phyCORE-AM57x System on Module Connectivity to the Carrier Board                | 54 |

| Figure 12. Power Scheme                                                                    | 55 |

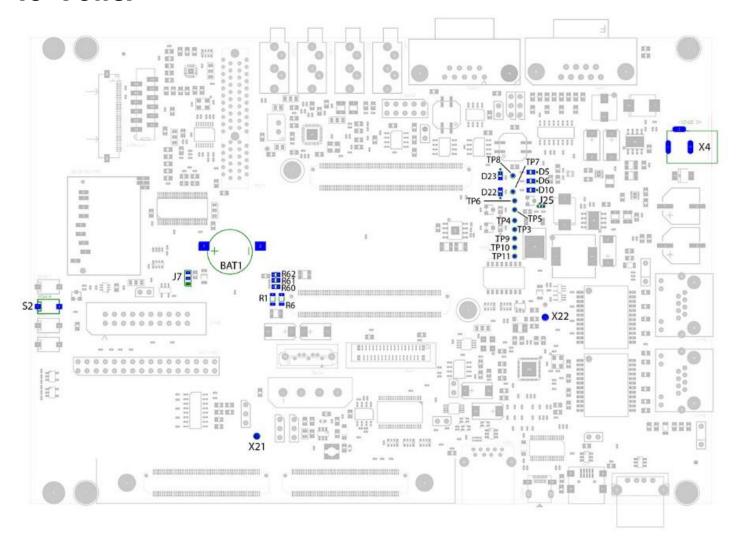

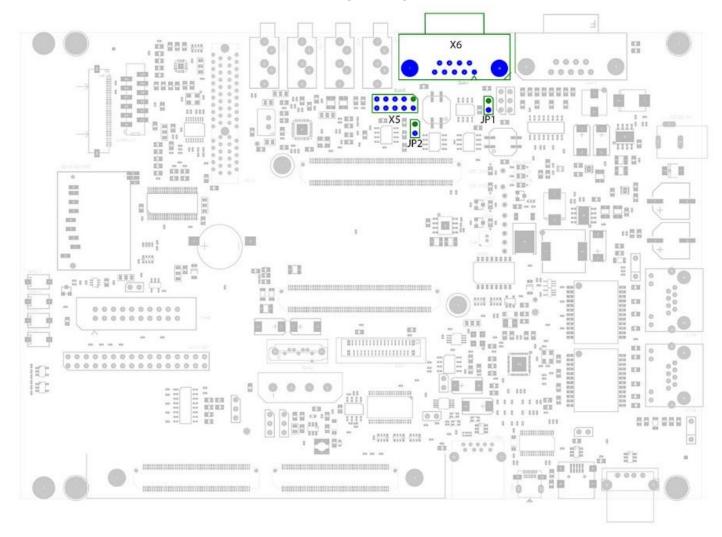

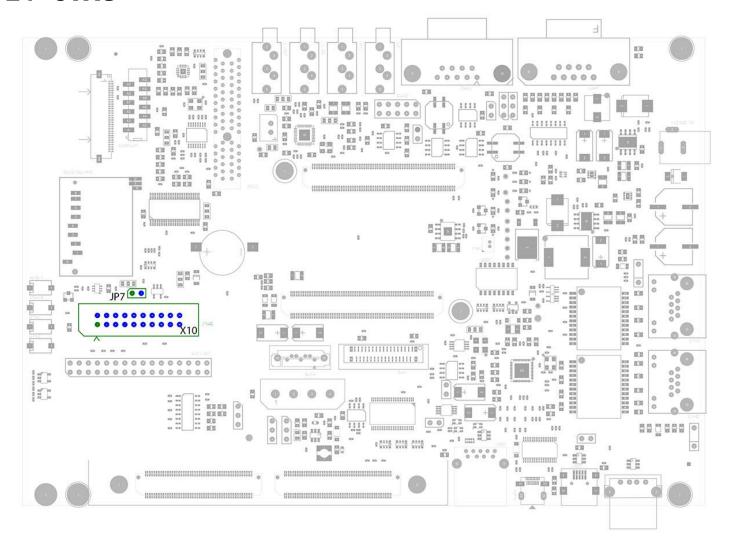

| Figure 13. CAN Connectors and Jumpers                                                      | 58 |

| Figure 14. SDIO/SD/MMC Connectors and Jumpers                                              | 60 |

| Figure 15. WiFi/Bluetooth Connector                                                        | 61 |

| Figure 16. Ethernet Connectors                                                             | 63 |

| Figure 17. USB Connectors and Jumpers                                                      | 65 |

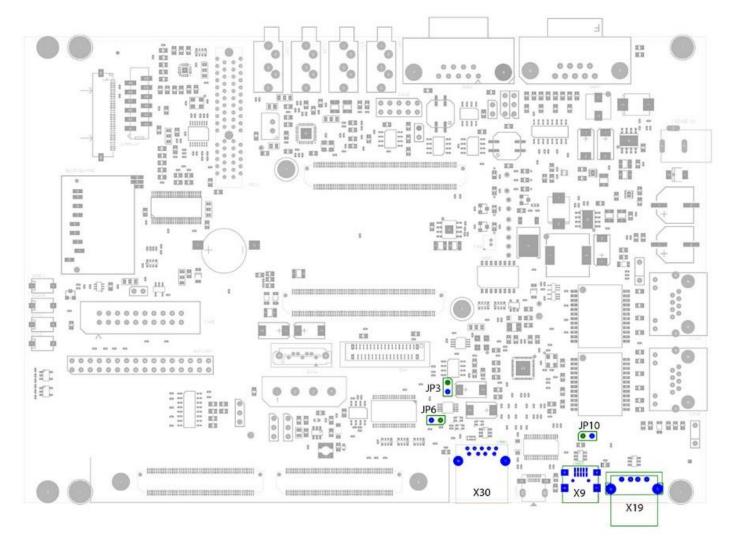

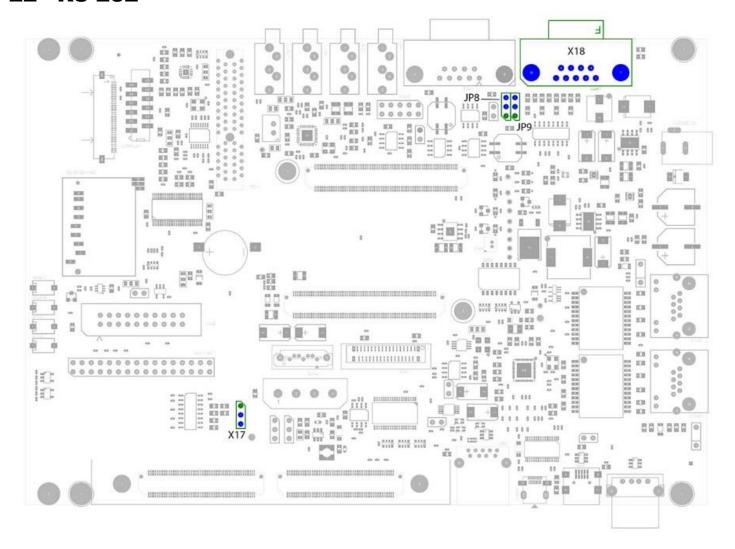

| Figure 18. RS-232 Connectors                                                               | 67 |

| Figure 19. DB9 RS-232 Connector X18 (UART 3) Pin Numbering                                 | 68 |

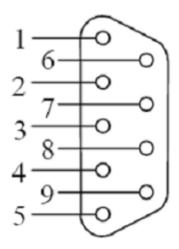

| Figure 20. SATA Power and Signal Connectors                                                | 70 |

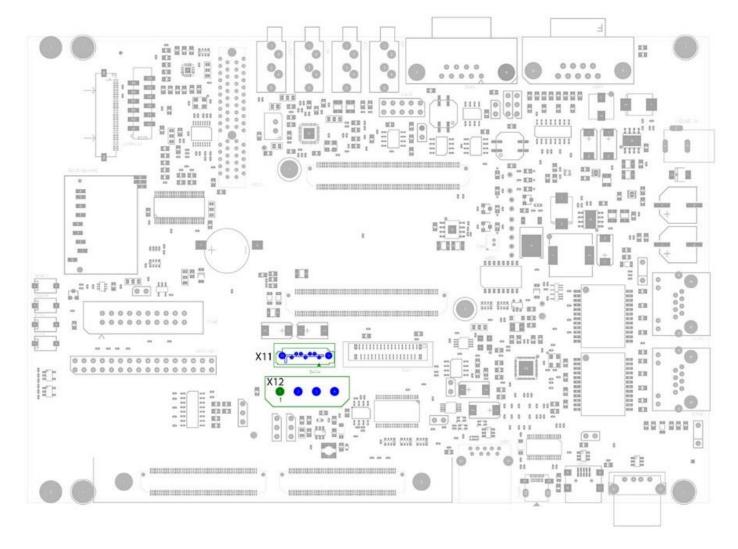

| Figure 21. JTAG Debug Connector                                                            | 72 |

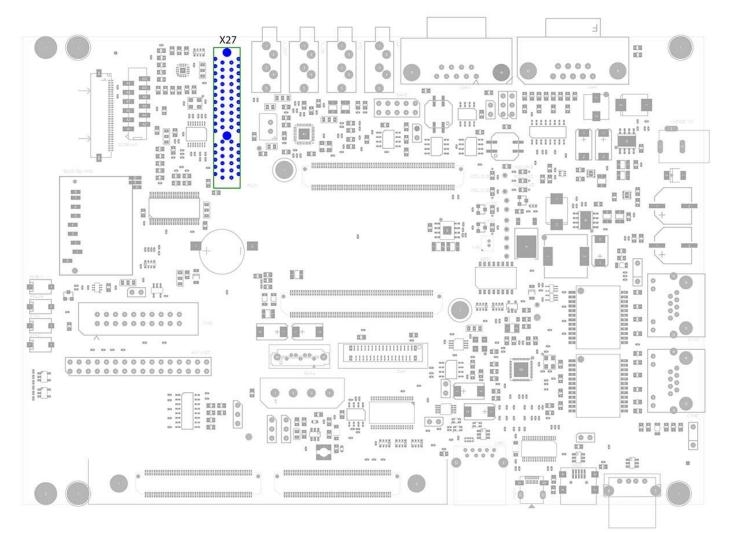

| Figure 22. PCIe Connector                                                                  | 74 |

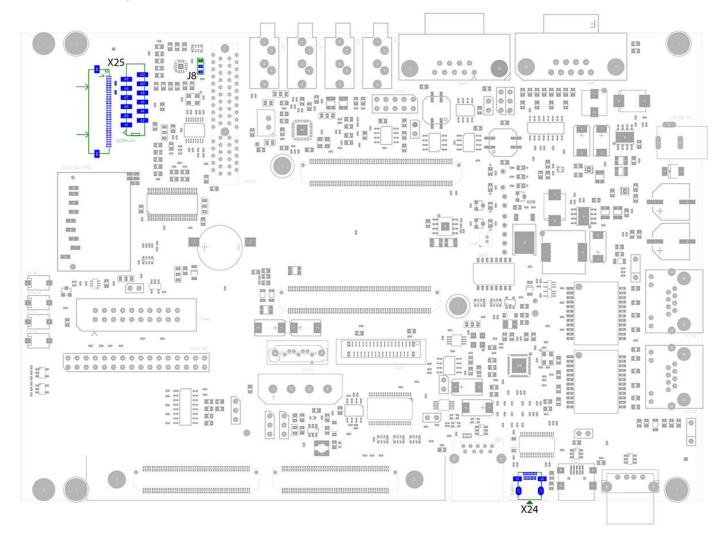

| Figure 23. Display Connectors and Jumpers                                                  | 76 |

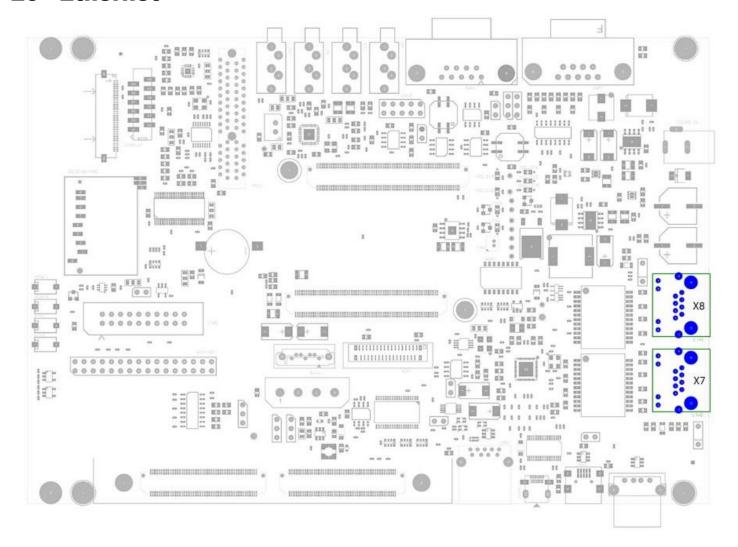

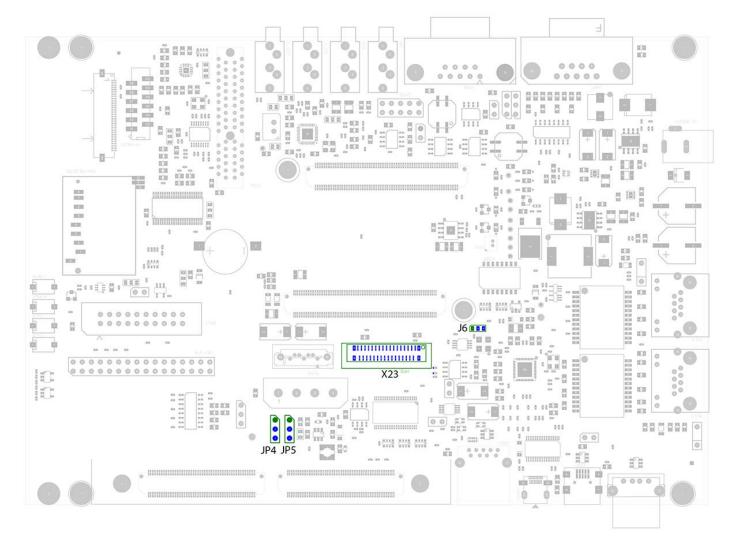

| Figure 24. Camera Interface Connectors and Jumpers                                         | 80 |

| Figure 25. Audio Interface Connectors and Jumpers                                          | 81 |

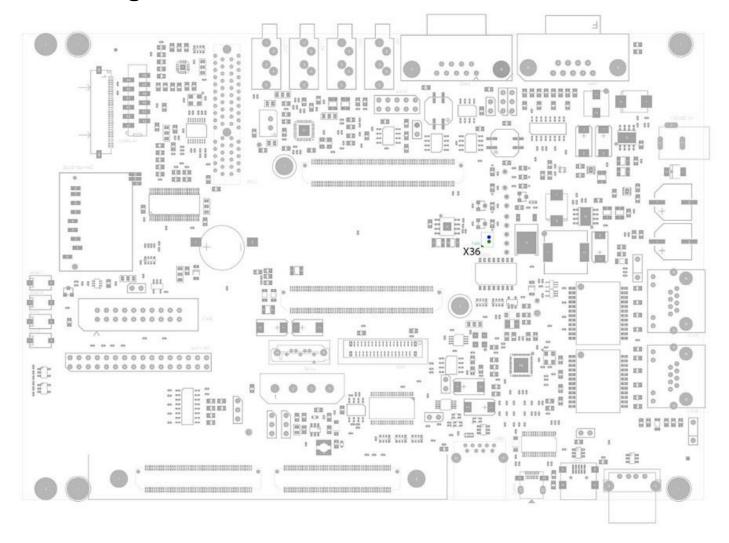

| Figure 26. Cooling Fan Connector                                                           | 83 |

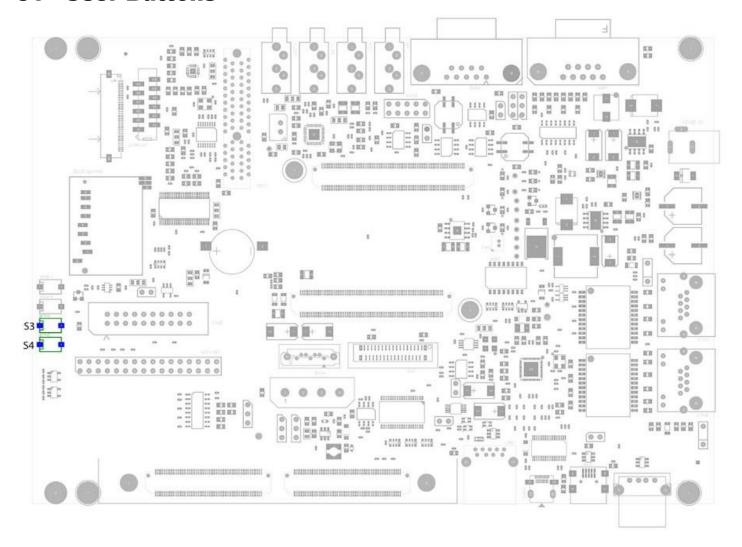

| Figure 27. User Buttons                                                                    | 84 |

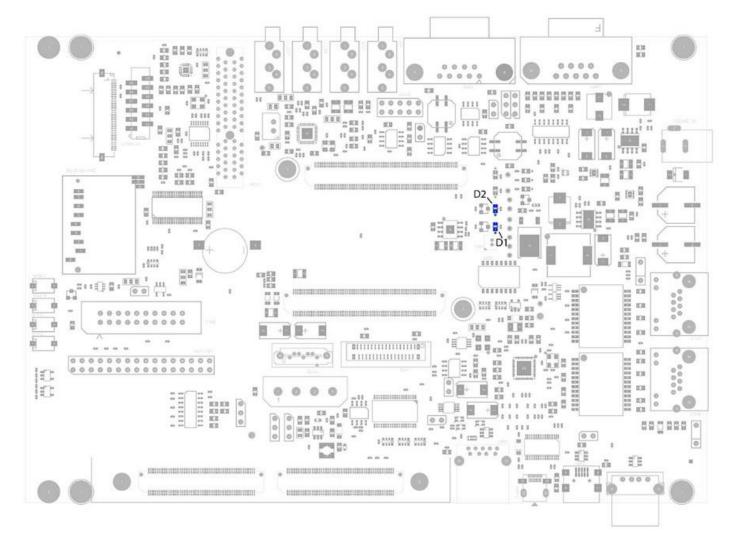

| Figure 28. User LEDs                                                                       | 85 |

| Figure 29. Boot Mode Selection                                                             | 86 |

| Figure 30. System Reset Button                                                             | 88 |

| Figure 31. GPIO Expansion Connector                                                        | 89 |

| Figure 32 PCM-957/GPIO Expansion Board Patch Field                                         | 91 |

## **List of Tables**

| Table 1. Abb  | reviations and Acronyms used in this Manual | 9  |

|---------------|---------------------------------------------|----|

|               | es of Signals                               |    |

|               | ORE-Connector (X1, X2) Pin-Out Description  |    |

|               | rnal Supply Voltages                        |    |

|               | rnal Voltage Rails                          |    |

|               | oot Signal Description                      |    |

|               | 1C for XIP/NAND Configuration               |    |

|               | undant SBL Image Offset                     |    |

|               | t Device Order                              |    |

| Table 10. Pin | Multiplexing According to Boot Peripheral   | 35 |

| Table 11. eM  | IMC Signal Connections to Processor         | 37 |

| Table 12. NA  | ND Flash Signal Connections to Processor    | 37 |

| Table 13. I2C | 1 Reserved Addresses                        | 41 |

| Table 14. Ted | chnical Specifications                      | 44 |

| Table 15. Op  | erating Characteristics                     | 44 |

| Table 16. Coi | nnectors and Headers                        | 48 |

| Table 17. But | ttons and Switches                          | 49 |

| Table 18. LED | Os                                          | 49 |

| Table 19. Sol | derless Jumper Settings                     | 52 |

| Table 20. Sol | der Jumper Settings                         | 53 |

| Table 21. Des | scription of Power Supply Test Pads         | 56 |

| Table 22. Des | scription of Power Supply Status LEDs       | 56 |

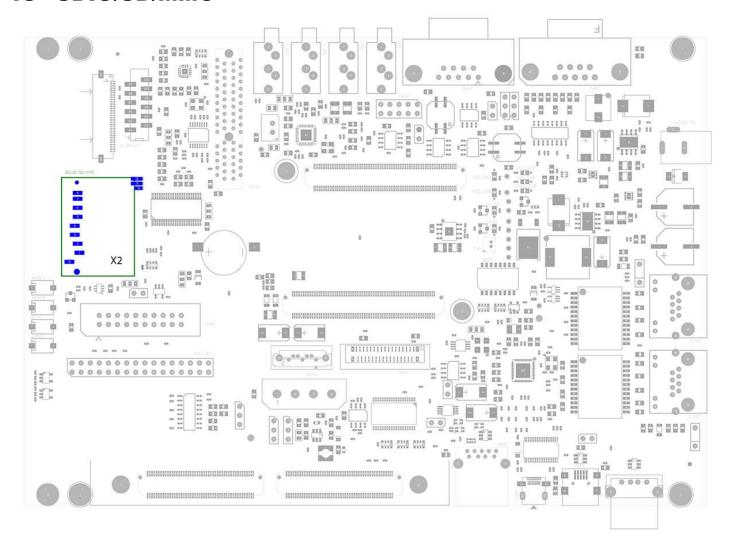

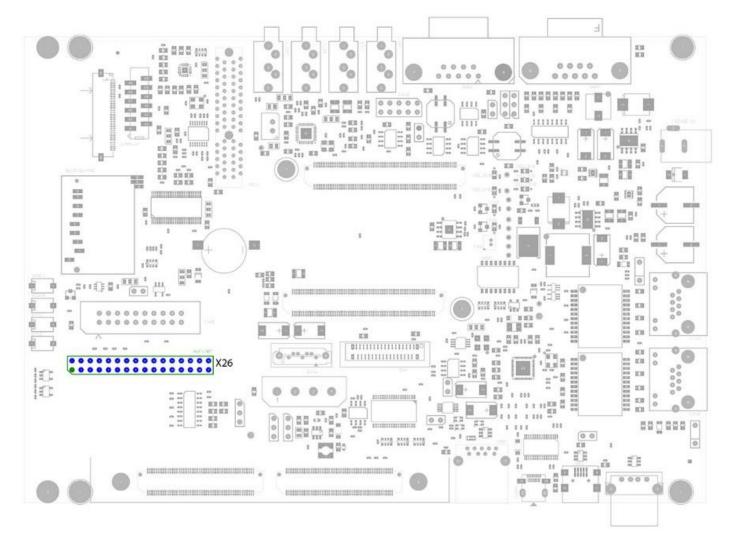

| Table 23. Wi  | Fi/Bluetooth Signals at X26                 | 61 |

| Table 24. Eth | ernet1 Default Strapping Options            | 64 |

| Table 25. UA  | RT3 DB9 (X18) Pin Description               | 68 |

| Table 26. UA  | RT5 Header (X17) Pin Description            | 68 |

| Table 27. SA  | ΓA Data Connector (X11) Pin Description     | 70 |

| Table 28. SA  | TA Power Connector (X12) Pin Description    | 71 |

| Table 29. JTA | G Connector (X10) Pin Description           | 73 |

| Table 30. PCI | e Connector (X27) Pin Description           | 74 |

| Table 31. Mid | cro-HDMI Connector (X24) Pin Description    | 76 |

| Table 32. LVI | OS Data Connector (X25) Pin Description     | 77 |

| Table 33. LVI | OS Power Connector (X25) Pin Description    | 78 |

|               | scription of Audio Connectors               |    |

|               | oling Fan Connector (X36) Pin Description   |    |

|               | ot Switch SYSBOOT[3:0] Settings             |    |

|               | ot Switch Configuration Description         |    |

|               | wer Signal Mapping                          |    |

|               | ntrol and Reset Signal Mapping              |    |

|               | MC Signal Mapping                           |    |

|               | IO Signal Mapping                           |    |

|               | I3A Signal Mapping                          |    |

|               | Signal Mapping                              |    |

|               | Signal Mapping                              |    |

| Table 45. QS  | PI1 Signal Mapping                          | 99 |

| Table 46. | KBD Signal Mapping              | 100 |

|-----------|---------------------------------|-----|

|           | PWM/Clock/Wakeup Signal Mapping |     |

|           | Document Revision History       |     |

## **Conventions, Abbreviations and Acronyms**

This hardware manual describes the PCM-057 System on Module in the following referred to as phyCORE-AM57x. The manual specifies the phyCORE-AM57x's design and function. Precise specifications for the Texas Instruments AM57x microcontrollers can be found in Texas Instrument's AM57x Data Sheet and Technical Reference Manual.

#### NOTE:

The BSP delivered with the phyCORE-AM57x usually includes drivers and/or software for controlling all components such as interfaces, memory, etc. Therefore, programming close to hardware at register level is not necessary in most cases. For this reason, this manual contains no detailed description of the controller's registers, or information relevant for software development. Please refer to the AM57x Reference Manual if such information is required.

#### **Conventions**

The conventions used in this manual are as follows:

- Signals that are preceded by an "n", "/", or "#" character (e.g.: nRD, /RD, or #RD), or that have a dash on top of the signal name (e.g.: RD) are designated as active low signals. That is, their active state is when they are driven low, or are driving low.

- A "0" indicates a logic zero or low-level signal, while a "1" represents a logic one or high-level signal.

- The hex-numbers given for addresses of I<sup>2</sup>C devices always represent the 7 MSB of the address byte. The correct value of the LSB which depends on the desired command (read (1), or write (0)) must be added to get the complete address byte. E.g. given address in this manual 0x41 => complete address byte = 0x83 to read from the device and 0x82 to write to the device.

- Tables which describe jumper settings show the default position in **bold text**

- Text in blue italic indicates a hyperlink within, or external to the document. Click these links to quickly jump to the applicable URL, part, chapter, table, or figure.

- References made to the phyCORE-Connector always refer to the high density Samtec connectors on the undersides of the phyCORE-AM57x

## **Abbreviations and Acronyms**

Many acronyms and abbreviations are used throughout this manual. Use the table below to navigate unfamiliar terms used in this document.

Table 1. Abbreviations and Acronyms used in this Manual

| Abbreviation | Definition                                                                                       |  |  |  |

|--------------|--------------------------------------------------------------------------------------------------|--|--|--|

| BSP          | Board Support Package (Software delivered with the Development Kit including an operating system |  |  |  |

|              | (Windows or Linux) preinstalled on the module and Development Tools).                            |  |  |  |

| СВ           | Carrier Board; used in reference to the phyCORE-AM57x Development Kit Carrier Board.             |  |  |  |

| DFF          | D flip-flop                                                                                      |  |  |  |

| EMB          | External memory bus                                                                              |  |  |  |

| EMI          | Electromagnetic interference                                                                     |  |  |  |

| GPI          | General purpose input                                                                            |  |  |  |

| GPIO         | General purpose input and output                                                                 |  |  |  |

| GPO          | General purpose output                                                                           |  |  |  |

| Abbreviation | Definition                                                                                                               |

|--------------|--------------------------------------------------------------------------------------------------------------------------|

| IRAM         | Internal RAM; the internal static RAM on the Texas Instruments AM57x microcontroller                                     |

| J            | Solder jumper; these types of jumpers require solder equipment to remove and place                                       |

| JP           | Solderless jumper; these types of jumpers can be removed and placed by hand with no special tools                        |

| PCB          | Printed circuit board                                                                                                    |

| PDI          | PHYTEC Display Interface; defined to connect PHYTEC display adapter boards, or custom adapters                           |

| PEB          | PHYTEC Extension Board                                                                                                   |

| PMIC         | Power management IC                                                                                                      |

| POR          | Power-on reset                                                                                                           |

| RTC          | Real-time clock                                                                                                          |

| SMT          | Surface mount technology                                                                                                 |

| SOM          | System on Module; used in reference to the PCM-057 / phyCORE-AM57x System on Module                                      |

| Sx           | User button Sx (e.g. S1, S2, etc.) used in reference to the available user buttons, or DIP switches on the Carrier Board |

| Sx_y         | Switch y of DIP switch Sx; used in reference to the DIP switch on the Carrier Board                                      |

| VBAT         | SOM standby voltage input                                                                                                |

Different types of signals are brought out at the phyCORE-Connector. The following table lists the abbreviations used to specify the type of a signal.

**Table 2. Types of Signals**

| Type of Signal            | Description                                                                 | Abbr.   |  |

|---------------------------|-----------------------------------------------------------------------------|---------|--|

| Power                     | Supply voltage                                                              | PWR     |  |

| Ref-Voltage               | Reference voltage                                                           | REF     |  |

| USB-Power                 | USB voltage                                                                 | USB     |  |

| Input                     | Digital input                                                               | IN      |  |

| Output                    | Digital output                                                              | OUT     |  |

| Input with pull up        | Input with pull-up, must only be connected to GND (jumper or open-collector | IPU     |  |

|                           | output).                                                                    |         |  |

| Input / output            | Bidirectional input / output                                                | Ю       |  |

| 5V Input with pulldown    | 5V tolerant input with pull-down                                            | 5V_PD   |  |

| 5V Input with pull-up     | 5V tolerant input with pull-up                                              | 5V_PU   |  |

| 3.3V Input with           | 3.3V tolerant input with pull-up                                            |         |  |

| Pull-up                   |                                                                             |         |  |

| 3.3V Input with pull-down | 3.3V tolerant input with pull-down                                          | 3V3_PD  |  |

| LVDS                      | Differential line pairs 100 Ohm LVDS                                        | LVDS    |  |

| Differential 90 Ohm       | Differential line pairs 90 Ohm                                              | DIFF90  |  |

| Differential 100 Ohm      | Differential line pairs 100 Ohm                                             | DIFF100 |  |

| Analog                    | Analog input or output                                                      | Analog  |  |

## **Preface**

This phyCORE-AM57x Hardware Manual describes the System on Module's design and functions. Precise specifications for the Texas Instruments AM57x processor can be found in the processor datasheet and/or technical reference manual (TRM).

## Declaration of Electro Magnetic Conformity of the PHYTEC phyCORE-AM57x System On Module

PHYTEC System on Modules (SOMs) are designed for installation in electrical appliances or, combined with the PHYTEC Carrier Board, can be used as dedicated Evaluation Boards (for use as a test and prototype platform for hardware/software development) in laboratory environments.

#### **CAUTION:**

PHYTEC products lacking protective enclosures are subject to damage by ESD and, hence, may only be unpacked, handled or operated in environments in which sufficient precautionary measures have been taken in respect to ESD-dangers. It is also necessary that only appropriately trained personnel (such as electricians, technicians and engineers) handle and/or operate these products. Moreover, PHYTEC products should not be operated without protection circuitry if connections to the product's pin header rows are longer than 3m.

PHYTEC products fulfill the norms of the European Union's Directive for Electro Magnetic Conformity only in accordance to the descriptions and rules of usage indicated in this hardware manual (particularly in respect to the pin header row connectors, power connector and serial interface to a host-PC).

#### NOTE:

Implementation of PHYTEC products into target devices, as well as user modifications and extensions of PHYTEC products, is subject to renewed establishment of conformity to, and certification of, Electro Magnetic Directives. Users should ensure conformance following any modifications to the products as well as implementation of the products into target systems.

The phyCORE-AM57x is one of a series of PHYTEC System on Modules that can be populated with different controllers and, hence, offers various functions and configurations. PHYTEC supports a variety of 8-/16- and 32-bit controllers in two ways:

- 1. As the basis for Rapid Development Kits which serve as a reference and evaluation platform.

- 2. As insert-ready, fully functional phyCORE OEM modules, which can be embedded directly into the user's peripheral hardware design.

Implementation of an OEM-able SOM subassembly as the "core" of your embedded design allows you to focus on hardware peripherals and firmware without expending resources to "re-invent" microcontroller circuitry. Furthermore, much of the value of the phyCORE module lies in its layout and test.

Production-ready Board Support Packages (BSPs) and Design Services for our hardware further reduce development time and expenses. Take advantage of PHYTEC products to shorten time-to-market, reduce development costs, and avoid substantial design issues and risks. For more information go to:

http://phytec.com/contact/

## **Product Change Management**

In addition to our HW and SW offerings, the buyer will receive a free obsolescence maintenance service for the HW provided when purchasing a PHYTEC SOM.

Our Product Change Management Team of developers is continuously processing all incoming PCN's (Product Change Notifications) from vendors and distributors concerning parts which are being used in our products. Possible impacts to the functionality of our products, due to changes of functionality or obsolesce of a certain part, are evaluated in order to take the right measures in purchasing or within our HW/SW design.

Our general philosophy here is: We never discontinue a product as long as there is demand for it. Therefore a set of methods has been established to fulfill our philosophy:

#### **Avoidance Strategies**

- Avoid changes by evaluating longevity of a parts during design-in phase.

- Ensure availability of equivalent second source parts.

- Maintain close contact with part vendors for awareness of roadmap strategies.

#### **Change Management in Case of Functional Changes**

- Avoid impacts on Product functionality by choosing equivalent replacement parts.

- Avoid impacts on Product functionality by compensating changes through HW redesign or backward compatibility

#### **SW Maintenance**

• Provide early change notifications concerning functional relevant changes of our Products.

#### Change Management in Rare Event of an Obsolete and Non-Replaceable Part

- Ensure long term availability by stocking parts through last time buy management, according to product forecasts.

- Offer long term frame contract to customers.

We refrain from providing detailed, part-specific information within this manual, which is subject to changes, due to ongoing part maintenance for our products.

## Part I: PCM-057/phyCORE-AM57x System on Module

Part I of this three-part manual provides detailed information on the phyCORE-AM57x System on Module (SOM) designed for custom integration into customer applications. The information in the following chapters is applicable to the 1428.3 PCB revision of the phyCORE-AM57x SOM.

## 1 Introduction

The phyCORE-AM57x belongs to PHYTEC's phyCORE System on Module family. The phyCORE SOMs represent the continuous development of PHYTEC System on Module technology. Like its mini-, micro- and nanoMODULE predecessors, the phyCORE boards integrate all core elements of a microcontroller system on a subminiature board and are designed in a manner that ensures their easy expansion and embedding in peripheral hardware development.

Independent research indicates that approximately 70% of all EMI (Electro Magnetic Interference) problems stem from insufficient supply voltage grounding of electronic components in high frequency environments. The phyCORE board design features an increased pin package that allows dedication of approximately 20% of all connector pins on the phyCORE boards to ground. This improves EMI and EMC characteristics, making it easier to design complex applications meeting EMI and EMC guidelines using phyCORE boards in high noise environments.

phyCORE boards achieve their small size through modern SMD technology and multi-layer design. In accordance with the complexity of the module, 0402-packaged SMD components and laser-drilled microvias are implemented, providing phyCORE users with access to this cutting-edge miniaturization technology for integration into their own design.

The phyCORE-AM57x is a subminiature (45 mm x 55 mm) insert-ready System on Module populated with the Texas Instruments AM57x microcontroller. Its universal design enables its insertion in a wide range of embedded applications. All controller signals and ports extend from the controller to high-density pitch (0.5 mm) connectors aligning two sides of the board, allowing it to be inserted like a "big chip" into a target application.

Precise specifications for the controller populating the board can be found in the applicable controller Technical Reference Manual or datasheet. The descriptions in this manual are based on the Texas Instruments AM57x. A description of compatible microcontroller derivative functions is not included, as such functions are not relevant for the basic functioning of the phyCORE-AM57x.

The phyCORE-AM57x offers the following features:

- Insert-ready, sub-miniature (45 mm x 55 mm) System on Module (SOM) subassembly in low EMI design, achieved through advanced SMD technology

- Populated with the Texas Instruments AM57x microcontroller (23 x 23mm, 0.8-mm Pitch, 760 Pin BGA)

- Dual ARM® Cortex™-A15 at max. 1.5 GHz clock frequency

- Dual C66x DSP

- Dual PRU-ICSS

- Dual ARM® Cortex™-M4 (general purpose usage)

- Image and Video Accelerator IVA-HD 1080p

- 3D Graphics Processing Unit (SGX544)

- 2D Graphics Accelerator (GC320)

- Boot from eMMC, NAND Flash, or SPI Flash

- General-Purpose Memory Controller Bus (GPMC): flexible 8/16-bit asynchronous memory interface with up to 8 chip-select signals.

- Up to 4 GB DDR3/3L (2 GB w/ECC)

- Up to 2 GB NAND or 32 GB eMMC

- Up to 32 KB EEPROM

- Up to 32 MB QSPI NOR

- 2x High speed MMC/SD/SDIO

- 2x PCle Gen2

- SATA/SATA2 up to 3Gbps

- 8x UARTs at TTL level

- 5x I<sup>2</sup>C

- 6x MCASP Audio ports

- 4x SPI

- 2x DCAN

- 1x USB 3.0 Dual Role and 1 USB 2.0 Dual Role

- 1x 10/100/1000 MBit Ethernet interface with on SOM Ethernet PHY allowing for direct connection to an Ethernet network

- 1x 10/100/1000 RGMII Ethernet interface. The TTL-level interface is available at the phyCORE connector.

- 3x LCD Interface Display Driver with an integrated touch interface and up to 24 data bits at 1080p Full HD (1920x1080)

- 1x HDMI at 1080p Full HD (1920x1080)

- 3x Parallel camera interfaces

- On-board power management IC with integrated RTC

- Support of standard 20 pin debug interface through JTAG connector

- Ultra-low power off-chip RTC

- Watchdog Timer, PWM, GPIO, and Keyboard

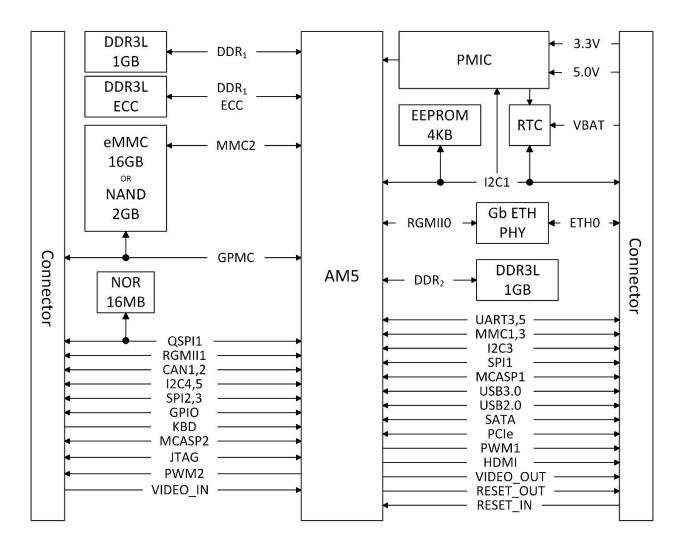

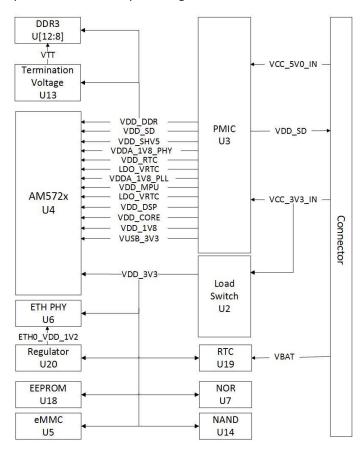

## 1.1 Block Diagram

Figure 1. phyCORE-AM57x Block Diagram

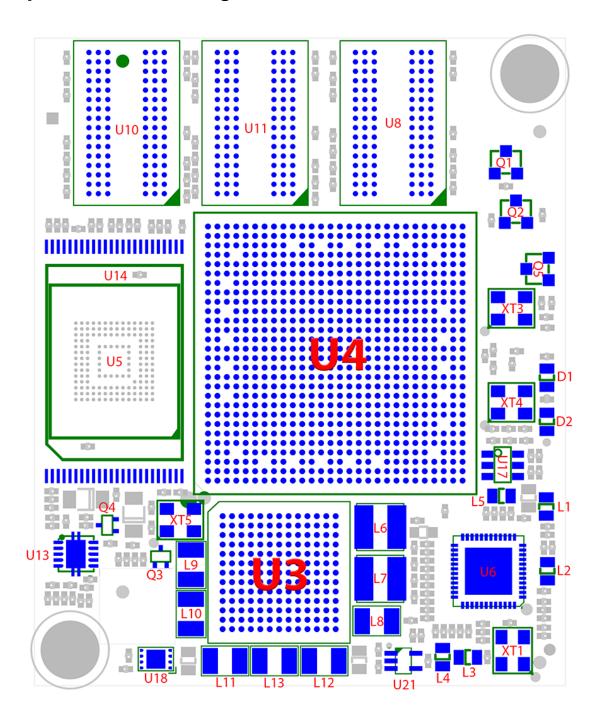

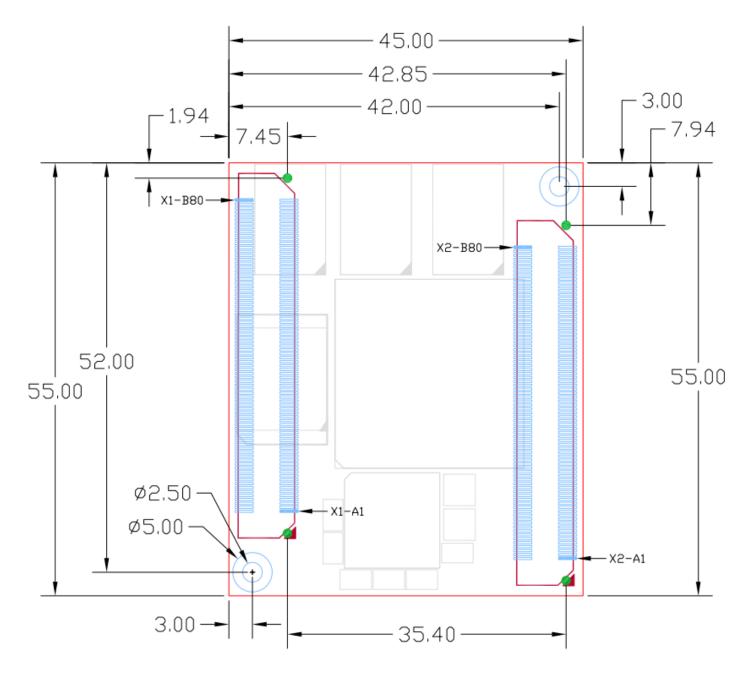

## 1.2 Component Placement Diagram

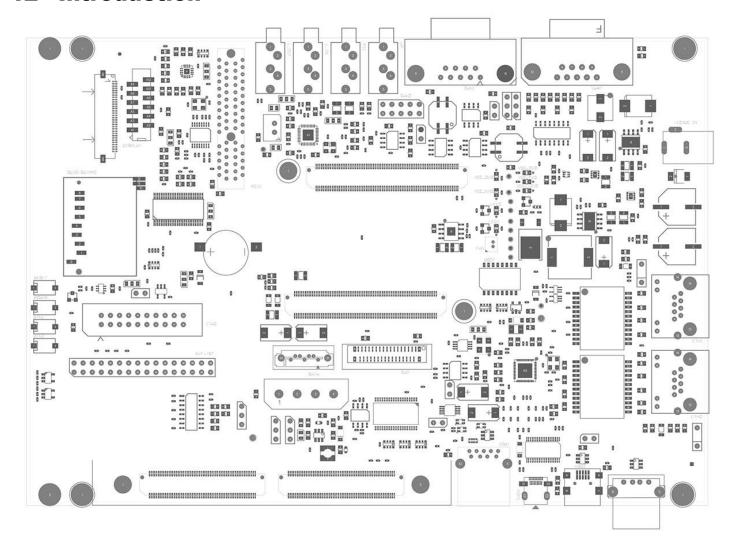

Figure 2. phyCORE-AM57x Component Placement (top view)

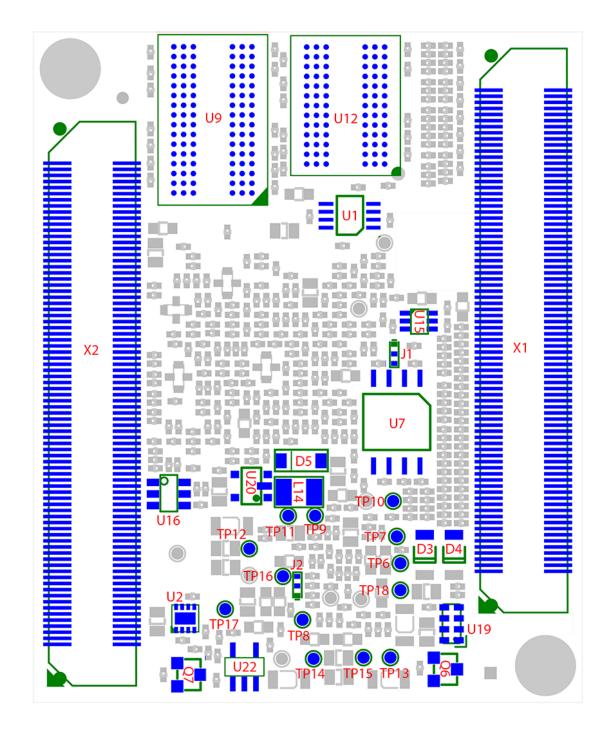

Figure 3. phyCORE-AM57x Component Placement (bottom view)

## 2 Pin Description

Please note that all module connections are not to exceed their expressed maximum voltage or current. Maximum signal input values are indicated in the corresponding controller manuals/data sheets. As damage from improper connections varies according to use and application, it is the user's responsibility to take appropriate safety measures to ensure that the module connections are protected from overloading through connected peripherals.

All controller signals extend to surface mount technology (SMT) connectors (0.5 mm) lining two sides of the module (referred to as the phyCORE-Connector). This allows the phyCORE-AM57x to be inserted into any target application like a "big chip".

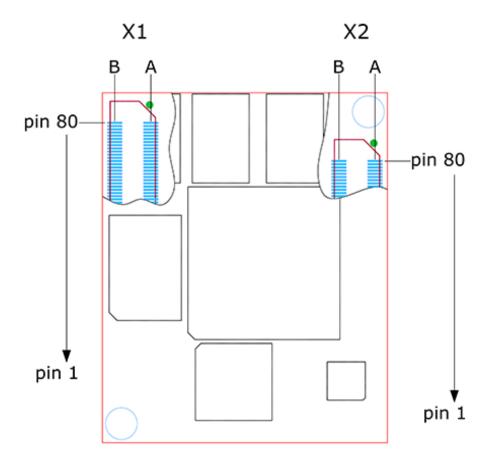

The numbering scheme for the phyCORE-Connector is based on a two-dimensional matrix in which column positions are identified by a letter and row position by a number. Pin 1A, for example, is located in the lower right hand corner of the matrix looking down through the top of the SOM. The pin numbering values decrease moving down on the board. Lettering of the pin connector columns progresses alphabetically from right to left for each connector (refer to Figure 4).

The numbered matrix can be aligned with the phyCORE-AM57x (viewed from above; phyCORE-Connector pointing down) or with the socket of the corresponding phyCORE Carrier Board/user target circuitry. The lower right-hand corner of the numbered matrix (pin A1) is thus covered with the corner of the phyCORE-AM57x marked with a triangle. The numbering scheme is always in relation to the PCB as viewed from above, even if all connector contacts extend to the bottom of the module.

The following figure illustrates the numbered matrix system. It shows a phyCORE-AM57x with SMT phyCORE Connectors on its underside (defined with dotted lines) as it would be mounted on a Carrier Board. To facilitate understanding of the pin assignment scheme, the diagram presents a cross-view of the phyCORE-module showing these phyCORE-Connectors mounted on the underside of the module's PCB.

Figure 4. Pinout of the phyCORE-Connector (top view, with cross section insert)

Table 3 provides an overview of the pinout of the phyCORE-Connector with signal names and descriptions specific to the phyCORE-AM57x. It also provides the appropriate signal level interface voltages listed in the Level column, along with the signal direction.

#### **CAUTION:**

Most of the controller pins have multiple multiplexed functions. Because most of these pins are connected directly to the phyCORE-Connector the functions are also available at the connector. Signal names and descriptions in Table 3, however, are regarding the specification of the phyCORE-AM57x and the functions defined therein. Please refer to the AM57x datasheet, or the schematic to learn about alternative functions. To utilize a specific pin's alternative, function the corresponding registers must be configured within the appropriate driver of the BSP. To support all features of the phyCORE-AM57x Carrier Board a few changes have been made in the BSP delivered with the module.

The Texas Instruments AM57x is a multi-voltage operated microcontroller and as such special attention should be paid to the interface voltage levels to avoid unintentional damage to the microcontroller and other on-board components. Please refer to the Texas Instruments AM57x Reference Manual for details on the functions and features of controller signals and port pins.

Table 3. phyCORE-Connector (X1, X2) Pin-Out Description

|      |                 |      | X1. ( | Column A                                                  |

|------|-----------------|------|-------|-----------------------------------------------------------|

| Pin# | Signal          | Туре | Level | Description                                               |

| A1   | X_DCAN1_RX      | IN   | 3.3V  | DCAN Receive Signal                                       |

| A2   | X DCAN1 TX      | OUT  | 3.3V  | DCAN Transmit Signal                                      |

| A3   | X_QSPI1_RTCLK   | IN   | 3.3 7 | QSPI return clock, the qspi1_sclk output must be          |

| 7.0  | X_QSI II_KI CEK |      |       | connected to the qspi1_rtclk input, and is used for       |

|      |                 |      |       | controlling the timing of the read                        |

|      |                 |      |       | return data.                                              |

| A4   | GND             | -    | -     |                                                           |

| A5   | X_QSPI1_D3      | IN   | 3.3V  | QSPI data input                                           |

| A6   | X_QSPI1_D2      | IN   | 3.3V  | QSPI data input                                           |

| A7   | X_QSPI1_D0      | 10   | 3.3V  | QSPI data input/output                                    |

| A8   | X_QSPI1_D1      | IN   | 3.3V  | QSPI data input                                           |

| A9   | GND             | -    | -     | Ground 0 V                                                |

| A10  | X_GPMC_AD4/     | 10   | 3.3V  | General Purpose Memory Controller Interface Address/Data  |

|      | SYSBOOT4        |      |       |                                                           |

| A11  | X_GPMC_AD5/     | 10   | 3.3V  | General Purpose Memory Controller Interface Address/Data  |

|      | SYSBOOT5        |      |       |                                                           |

| A12  | X GPMC AD6/     | 10   | 3.3V  | General Purpose Memory Controller Interface Address/Data  |

|      | SYSBOOT6        |      |       |                                                           |

| A13  | X GPMC AD7/     | 10   | 3.3V  | General Purpose Memory Controller Interface Address/Data  |

|      | SYSBOOT7        |      |       |                                                           |

| A14  | GND             | -    | -     | Ground 0 V                                                |

| A15  | X_GPMC_AD12/    | Ю    | 3.3V  | General Purpose Memory Controller Interface Address/Data  |

|      | SYSBOOT12       |      |       |                                                           |

| A16  | X_GPMC_AD13/    | 10   | 3.3V  | General Purpose Memory Controller Interface Address/Data  |

|      | SYSBOOT13       |      |       |                                                           |

| A17  | X_GPMC_AD14/    | 10   | 3.3V  | General Purpose Memory Controller Interface Address/Data  |

|      | SYSBOOT14       |      |       |                                                           |

| A18  | X_GPMC_AD15/    | 10   | 3.3V  | General Purpose Memory Controller Interface Address/Data  |

|      | SYSBOOT15       |      |       |                                                           |

| A19  | GND             | -    | -     | Ground 0 V                                                |

| A20  | X_GPMC_ADVN_ALE | OUT  | 3.3V  | General Purpose Memory Controller Interface address valid |

|      |                 |      |       | / address latch enable                                    |

| A21  | X_GPMC_OEN_REN  | OUT  | 3.3V  | General Purpose Memory Controller output enable / read    |

|      |                 |      |       | enable                                                    |

| A22  | X_GPMC_WAIT0    | 10   | 3.3V  | General Purpose Memory Controller WAIT                    |

| A23  | X_GPMC_WEN      | OUT  | 3.3V  | General Purpose Memory Controller write enable            |

| A24  | GND             | -    | -     | Ground 0 V                                                |

| A25  | X_RGMII1_TXD3   | OUT  | 3.3V  | Ethernet 1 RGMII Transmit data                            |

| A26  | X_RGMII1_TXD2   | OUT  | 3.3V  | Ethernet 1 RGMII Transmit data                            |

| A27  | X_RGMII1_TXD1   | OUT  | 3.3V  | Ethernet 1 RGMII Transmit data                            |

| A28  | X_RGMII1_TXD0   | OUT  | 3.3V  | Ethernet 1 RGMII Transmit data                            |

| A29  | GND             | -    | -     | Ground 0 V                                                |

| A30  | X_RGMII1_RXD1   | IN   | 3.3V  | Ethernet 1 RGMII Receive data                             |

| A31  | X_RGMII1_RXD0   | IN   | 3.3V  | Ethernet 1 RGMII Receive data                             |

| A32  | X_KBD_ROW2      | IN   | 3.3V  | Keypad row                                                |

|       | X1, Column A |      |       |                                                              |  |  |  |

|-------|--------------|------|-------|--------------------------------------------------------------|--|--|--|

| Pin # | Signal       | Туре | Level | Description                                                  |  |  |  |

| A33   | X KBD ROW3   | IN   | 3.3V  | Keypad row                                                   |  |  |  |

| A34   | GND          | -    | -     | Ground 0 V                                                   |  |  |  |

| A35   | X KBD COL2   | OUT  | 3.3V  | Keypad column                                                |  |  |  |

| A36   | X KBD COL3   | OUT  | 3.3V  | Keypad column                                                |  |  |  |

| A37   | X_I2C4_SCL   | 10   | 3.3V  | I <sup>2</sup> C bus 4 clock                                 |  |  |  |

| A38   | X I2C4 SDA   | 10   | 3.3V  | I <sup>2</sup> C bus 4 data                                  |  |  |  |

| A39   | GND          | -    | -     | Ground 0 V                                                   |  |  |  |

| A40   | X_SPI3_CS0n  | OUT  | 3.3V  | SPI 3 chip select 0, (active low)                            |  |  |  |

| A41   | X_SPI3_CLK   | 10   | 3.3V  | SPI3 Clock                                                   |  |  |  |

| A42   | X_SPI3_DIN   | IN   | 3.3V  | SPI3 Data in                                                 |  |  |  |

| A43   | X_SPI3_DO    | OUT  | 3.3V  | SPI3 Data out                                                |  |  |  |

| A44   | GND          | -    | -     | Ground 0 V                                                   |  |  |  |

| A45   | X_WAKEUP2    | IN   | 3.3V  | External wake-up signal                                      |  |  |  |

| A46   | X_GPIO4_3    | 10   | 3.3V  | AM57x GPIO4_3                                                |  |  |  |

| A47   | X_GPIO4_19   | 10   | 3.3V  | AM57x GPIO4_19                                               |  |  |  |

| A48   | X_XREF_CLK3  | IN   | 3.3V  | External Reference Clock 3. For Audio and other Peripherals. |  |  |  |

| A49   | GND          | -    | -     | Ground 0 V                                                   |  |  |  |

| A50   | X_GPIO1_26   | Ю    | 3.3V  | AM57x GPIO1_26                                               |  |  |  |

| A51   | X_GPIO1_27   | 10   | 3.3V  | AM57x GPIO1_27                                               |  |  |  |

| A52   | X_GPIO1_28   | 10   | 3.3V  | AM57x GPIO1_28                                               |  |  |  |

| A53   | X_GPIO1_29   | 10   | 3.3V  | AM57x GPIO1_29                                               |  |  |  |

| A54   | GND          | -    | -     | Ground 0 V                                                   |  |  |  |

| A55   | X_GPIO2_2    | 10   | 3.3V  | AM57x GPIO2_2                                                |  |  |  |

| A56   | X_GPIO7_5    | 10   | 3.3V  | AM57x GPIO7_5                                                |  |  |  |

| A57   | X_GPIO6_4    | Ю    | 3.3V  | AM57x GPIO6_4                                                |  |  |  |

| A58   | X_GPIO8_2    | 10   | 3.3V  | AM57x GPIO8_2                                                |  |  |  |

| A59   | GND          | -    | -     | Ground 0 V                                                   |  |  |  |

| A60   | X_GPIO8_20   | 10   | 3.3V  | AM57x GPIO8_20                                               |  |  |  |

| A61   | X_GPIO8_21   | Ю    | 3.3V  | AM57x GPIO8_21                                               |  |  |  |

| A62   | X_GPIO8_22   | 10   | 3.3V  | AM57x GPIO8_22                                               |  |  |  |

| A63   | X_GPIO8_23   | 10   | 3.3V  | AM57x GPIO8_23                                               |  |  |  |

| A64   | GND          | -    | -     | Ground 0 V                                                   |  |  |  |

| A65   | X_VIN3A_D4   | IN   | 3.3V  | Video Input 3 Port A Data input                              |  |  |  |

| A66   | X_VIN3A_D5   | IN   | 3.3V  | Video Input 3 Port A Data input                              |  |  |  |

| A67   | X_VIN3A_D6   | IN   | 3.3V  | Video Input 3 Port A Data input                              |  |  |  |

| A68   | X_VIN3A_D7   | IN   | 3.3V  | Video Input 3 Port A Data input                              |  |  |  |

| A69   | GND          | -    | -     | Ground 0 V                                                   |  |  |  |

| A70   | X_VIN3A_D12  | IN   | 3.3V  | Video Input 3 Port A Data input                              |  |  |  |

| A71   | X_VIN3A_D13  | IN   | 3.3V  | Video Input 3 Port A Data input                              |  |  |  |

| A72   | X_VIN3A_D14  | IN   | 3.3V  | Video Input 3 Port A Data input                              |  |  |  |

| A73   | X_VIN3A_D15  | IN   | 3.3V  | Video Input 3 Port A Data input                              |  |  |  |

| A74   | GND          | -    | -     | Ground 0 V                                                   |  |  |  |

| A75   | X_VIN3A_CLK0 | IN   | 3.3V  | Video Input 3 Port A Clock input                             |  |  |  |

| A76   | X_XREF_CLK0  | IN   | 3.3V  | External Reference Clock 0. For Audio and other Peripherals. |  |  |  |

| A77   | X_JTAG_TMS   | IN   | 3.3V  | JTAG Chain Test Mode Select signal                           |  |  |  |

| A78   | X_JTAG_TRSTn | IN   | 3.3V  | JTAG Chain Test Reset                                        |  |  |  |

| A79   | GND          | -    | -     | Ground 0 V                                                   |  |  |  |

|      | X1, Column A |      |       |                                     |  |  |

|------|--------------|------|-------|-------------------------------------|--|--|

| Pin# | Signal       | Туре | Level | Description                         |  |  |

| A80  | X_JTAG_RTCK  | OUT  | 3.3V  | JTAG Chain Return Test Clock signal |  |  |

|      | X1, Column B   |      |       |                                                               |  |  |  |  |

|------|----------------|------|-------|---------------------------------------------------------------|--|--|--|--|

| Pin# | Signal         | Туре | Level | Description                                                   |  |  |  |  |

| B1   | X_DCAN2_TX     | OUT  | 3.3V  | DCAN Transmit Signal                                          |  |  |  |  |

| B2   | GND            | -    | -     | Ground 0 V                                                    |  |  |  |  |

| В3   | X_DCAN2_RX     | IN   | 3.3V  | DCAN Receive Signal                                           |  |  |  |  |

| B4   | X_QSPI1_SCLK   | 10   | 3.3V  | QSPI1 Serial Clock Output                                     |  |  |  |  |

| B5   | X_QSPI1_CS0    |      |       | QSPI1 Chip Select [0]. This pin is Used for QSPI1 boot modes. |  |  |  |  |

|      |                |      |       | (active low)                                                  |  |  |  |  |

| В6   | X_QSPI1_CS1    |      |       | QSPI1 Chip Select[1] (active low)                             |  |  |  |  |

| В7   | GND            | -    | -     | Ground 0 V                                                    |  |  |  |  |

| B8   | X_GPMC_BEN0    | OUT  | 3.3V  | GPMC lower-byte enable active low                             |  |  |  |  |

| В9   | X_GPMC_BEN1    | OUT  | 3.3V  | GPMC upper-byte enable active low                             |  |  |  |  |

| B10  | X_GPMC_CLK     | 10   | 3.3V  | GPMC Clock output                                             |  |  |  |  |

| B11  | X_GPMC_CS0     | OUT  | 3.3V  | GPMC Chip Select 0 (active low)                               |  |  |  |  |

| B12  | GND            | -    | -     | Ground 0 V                                                    |  |  |  |  |

| B13  | X_GPMC_AD0/    | 10   | 3.3V  | General Purpose Memory Controller Interface Address/Data      |  |  |  |  |

|      | SYSBOOT0       |      |       |                                                               |  |  |  |  |

| B14  | X_GPMC_AD1/    | 10   | 3.3V  | General Purpose Memory Controller Interface Address/Data      |  |  |  |  |

|      | SYSBOOT1       |      |       |                                                               |  |  |  |  |

| B15  | X_GPMC_AD2/    | Ю    | 3.3V  | General Purpose Memory Controller Interface Address/Data      |  |  |  |  |

|      | SYSBOOT2       |      |       |                                                               |  |  |  |  |

| B16  | X_GPMC_AD3/    | Ю    | 3.3V  | General Purpose Memory Controller Interface Address/Data      |  |  |  |  |

|      | SYSBOOT3       |      |       |                                                               |  |  |  |  |

| B17  | GND            | -    | -     | Ground 0 V                                                    |  |  |  |  |

| B18  | X_GPMC_AD8/    | 10   | 3.3V  | General Purpose Memory Controller Interface Address/D         |  |  |  |  |

|      | SYSBOOT8       |      |       |                                                               |  |  |  |  |

| B19  | X_GPMC_AD9/    | 10   | 3.3V  | General Purpose Memory Controller Interface Address/Data      |  |  |  |  |

|      | SYSBOOT9       |      |       |                                                               |  |  |  |  |

| B20  | X_GPMC_AD10/   | Ю    | 3.3V  | General Purpose Memory Controller Interface Address/Data      |  |  |  |  |

|      | SYSBOOT10      | 1    |       |                                                               |  |  |  |  |

| B21  | X_GPMC_AD11/   | Ю    | 3.3V  | General Purpose Memory Controller Interface Address/Data      |  |  |  |  |

| 200  | SYSBOOT11      |      |       |                                                               |  |  |  |  |

| B22  | GND            | -    | -     | Ground 0 V                                                    |  |  |  |  |

| B23  | X_MDIO_D       | IO   | 3.3V  | Ethernet MDIO interface data                                  |  |  |  |  |

| B24  | X_MDIO_MCLK    | OUT  | 3.3V  | Ethernet MDIO interface clock                                 |  |  |  |  |

| B25  | X_RGMII1_TXC   | OUT  | 3.3V  | Ethernet 1 RGMII transmit clock                               |  |  |  |  |

| B26  | X_RGMII1_TXCTL | OUT  | 3.3V  | Ethernet 1 RGMII transmit control                             |  |  |  |  |

| B27  | GND            | -    | -     | Ground 0 V                                                    |  |  |  |  |

| B28  | X_RGMII1_RXC   | IN   | 3.3V  | Ethernet 1 RGMII Receive clock                                |  |  |  |  |

| B29  | X_RGMII1_RXCTL | IN   | 3.3V  | Ethernet 1 RGMII Receive control                              |  |  |  |  |

| B30  | X_RGMII1_RXD3  | IN   | 3.3V  | Ethernet 1 RGMII Receive data                                 |  |  |  |  |

| B31  | X_RGMII1_RXD2  | IN   | 3.3V  | Ethernet 1 RGMII Receive data                                 |  |  |  |  |

| B32  | GND            | -    | -     | Ground 0 V                                                    |  |  |  |  |

| B33  | X_KBD_ROW0     | IN   | 3.3V  | Keypad row                                                    |  |  |  |  |

| Pin #         Signal         Type         Level         Description           B34         X_KBD_ROW1         IN         3.3V         Keypad row           B35         X_KBD_COL0         OUT         3.3V         Keypad column           B36         X_KBD_COL1         OUT         3.3V         Keypad column           B37         GND         -         -         Ground 0 V           B38         X_I2C5_SDA         IO         3.3V         I²C bus 5 clock           B39         X_I2C5_SCL         IO         3.3V         I²C bus 5 data           B40         X_EHRPWM1B         OUT         3.3V         EHRPWM1 Output B           B41         X_SPI3_nCS1         IO         3.3V         SPI3 chip select 1, (active low)           B42         GND         -         -         Ground 0 V           B43         X_MCASP2_ACLKX         IO         3.3V         MCASP2 Transmit Bit Clock           B44         X_MCASP2_AXR2         IO         3.3V         MCASP3 Transmit/Receive Data           B45         X_MCASP2_FSX         IO         3.3V         MCASP3 Transmit Frame Sync |                                                   |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--|

| B34         X_KBD_ROW1         IN         3.3V         Keypad row           B35         X_KBD_COL0         OUT         3.3V         Keypad column           B36         X_KBD_COL1         OUT         3.3V         Keypad column           B37         GND         -         -         Ground 0 V           B38         X_I2C5_SDA         IO         3.3V         I²C bus 5 clock           B39         X_I2C5_SCL         IO         3.3V         I²C bus 5 data           B40         X_EHRPWM1B         OUT         3.3V         EHRPWM1 Output B           B41         X_SPI3_nCS1         IO         3.3V         SPI3 chip select 1, (active low)           B42         GND         -         -         Ground 0 V           B43         X_MCASP2_ACLKX         IO         3.3V         MCASP2 Transmit Bit Clock           B44         X_MCASP2_AXR2         IO         3.3V         MCASP3 Transmit/Receive Data           B45         X_MCASP2_FSX         IO         3.3V         MCASP3 Transmit Frame Sync                                                                               |                                                   |  |

| B35         X_KBD_COL0         OUT         3.3V         Keypad column           B36         X_KBD_COL1         OUT         3.3V         Keypad column           B37         GND         -         -         Ground 0 V           B38         X_I2C5_SDA         IO         3.3V         I²C bus 5 clock           B39         X_I2C5_SCL         IO         3.3V         I²C bus 5 data           B40         X_EHRPWM1B         OUT         3.3V         EHRPWM1 Output B           B41         X_SPI3_nCS1         IO         3.3V         SPI3 chip select 1, (active low)           B42         GND         -         -         Ground 0 V           B43         X_MCASP2_ACLKX         IO         3.3V         MCASP2 Transmit Bit Clock           B44         X_MCASP2_AXR2         IO         3.3V         MCASP3 Transmit/Receive Data           B45         X_MCASP2_FSX         IO         3.3V         MCASP3 Transmit Frame Sync                                                                                                                                                           |                                                   |  |

| B36         X_KBD_COL1         OUT         3.3V         Keypad column           B37         GND         -         -         Ground 0 V           B38         X_I2C5_SDA         IO         3.3V         I²C bus 5 clock           B39         X_I2C5_SCL         IO         3.3V         I²C bus 5 data           B40         X_EHRPWM1B         OUT         3.3V         EHRPWM1 Output B           B41         X_SPI3_nCS1         IO         3.3V         SPI3 chip select 1, (active low)           B42         GND         -         -         Ground 0 V           B43         X_MCASP2_ACLKX         IO         3.3V         MCASP2 Transmit Bit Clock           B44         X_MCASP2_AXR2         IO         3.3V         MCASP3 Transmit/Receive Data           B45         X_MCASP2_AXR3         IO         3.3V         MCASP3 Transmit Frame Sync                                                                                                                                                                                                                                          |                                                   |  |

| B37         GND         -         -         Ground 0 V           B38         X_I2C5_SDA         IO         3.3V         I²C bus 5 clock           B39         X_I2C5_SCL         IO         3.3V         I²C bus 5 data           B40         X_EHRPWM1B         OUT         3.3V         EHRPWM1 Output B           B41         X_SPI3_nCS1         IO         3.3V         SPI3 chip select 1, (active low)           B42         GND         -         -         Ground 0 V           B43         X_MCASP2_ACLKX         IO         3.3V         MCASP2 Transmit Bit Clock           B44         X_MCASP2_AXR2         IO         3.3V         MCASP3 Transmit/Receive Data           B45         X_MCASP2_AXR3         IO         3.3V         MCASP3 Transmit Frame Sync           B46         X_MCASP2_FSX         IO         3.3V         MCASP3 Transmit Frame Sync                                                                                                                                                                                                                            |                                                   |  |

| B38         X_I2C5_SDA         IO         3.3V         I²C bus 5 clock           B39         X_I2C5_SCL         IO         3.3V         I²C bus 5 data           B40         X_EHRPWM1B         OUT         3.3V         EHRPWM1 Output B           B41         X_SPI3_nCS1         IO         3.3V         SPI3 chip select 1, (active low)           B42         GND         -         -         Ground 0 V           B43         X_MCASP2_ACLKX         IO         3.3V         MCASP2 Transmit Bit Clock           B44         X_MCASP2_AXR2         IO         3.3V         MCASP3 Transmit/Receive Data           B45         X_MCASP2_AXR3         IO         3.3V         MCASP3 Transmit/Receive Data           B46         X_MCASP2_FSX         IO         3.3V         MCASP3 Transmit Frame Sync                                                                                                                                                                                                                                                                                           |                                                   |  |

| B39         X_I2C5_SCL         IO         3.3V         I²C bus 5 data           B40         X_EHRPWM1B         OUT         3.3V         EHRPWM1 Output B           B41         X_SPI3_nCS1         IO         3.3V         SPI3 chip select 1, (active low)           B42         GND         -         -         Ground 0 V           B43         X_MCASP2_ACLKX         IO         3.3V         MCASP2 Transmit Bit Clock           B44         X_MCASP2_AXR2         IO         3.3V         MCASP3 Transmit/Receive Data           B45         X_MCASP2_AXR3         IO         3.3V         MCASP3 Transmit/Receive Data           B46         X_MCASP2_FSX         IO         3.3V         MCASP3 Transmit Frame Sync                                                                                                                                                                                                                                                                                                                                                                            |                                                   |  |

| B40         X_EHRPWM1B         OUT         3.3V         EHRPWM1 Output B           B41         X_SPI3_nCS1         IO         3.3V         SPI3 chip select 1, (active low)           B42         GND         -         -         Ground 0 V           B43         X_MCASP2_ACLKX         IO         3.3V         MCASP2 Transmit Bit Clock           B44         X_MCASP2_AXR2         IO         3.3V         MCASP3 Transmit/Receive Data           B45         X_MCASP2_AXR3         IO         3.3V         MCASP3 Transmit/Receive Data           B46         X_MCASP2_FSX         IO         3.3V         MCASP3 Transmit Frame Sync                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                   |  |

| B41         X_SPI3_nCS1         IO         3.3V         SPI3 chip select 1, (active low)           B42         GND         -         -         Ground 0 V           B43         X_MCASP2_ACLKX         IO         3.3V         MCASP2 Transmit Bit Clock           B44         X_MCASP2_AXR2         IO         3.3V         MCASP3 Transmit/Receive Data           B45         X_MCASP2_AXR3         IO         3.3V         MCASP3 Transmit/Receive Data           B46         X_MCASP2_FSX         IO         3.3V         MCASP3 Transmit Frame Sync                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                   |  |

| B42         GND         -         -         Ground 0 V           B43         X_MCASP2_ACLKX         IO         3.3V         MCASP2 Transmit Bit Clock           B44         X_MCASP2_AXR2         IO         3.3V         MCASP3 Transmit/Receive Data           B45         X_MCASP2_AXR3         IO         3.3V         MCASP3 Transmit/Receive Data           B46         X_MCASP2_FSX         IO         3.3V         MCASP3 Transmit Frame Sync                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                   |  |

| B43X_MCASP2_ACLKXIO3.3VMCASP2 Transmit Bit ClockB44X_MCASP2_AXR2IO3.3VMCASP3 Transmit/Receive DataB45X_MCASP2_AXR3IO3.3VMCASP3 Transmit/Receive DataB46X_MCASP2_FSXIO3.3VMCASP3 Transmit Frame Sync                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                   |  |

| B44     X_MCASP2_AXR2     IO     3.3V     MCASP3 Transmit/Receive Data       B45     X_MCASP2_AXR3     IO     3.3V     MCASP3 Transmit/Receive Data       B46     X_MCASP2_FSX     IO     3.3V     MCASP3 Transmit Frame Sync                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                   |  |

| B45     X_MCASP2_AXR3     IO     3.3V     MCASP3 Transmit/Receive Data       B46     X_MCASP2_FSX     IO     3.3V     MCASP3 Transmit Frame Sync                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                   |  |

| B46 X_MCASP2_FSX IO 3.3V MCASP3 Transmit Frame Sync                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                   |  |

| B47 GND Ground 0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                   |  |

| B48 X_SPI2_nCS0 OUT 3.3V SPI 2 chip select 0, (active low)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                   |  |

| B49 X SPI2 DIN IN 3.3V SPI3 Data in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                   |  |

| B50 X_SPI2_DOUT OUT 3.3V SPI3 Data out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                   |  |

| B51 X_SPI2_CLK IO 3.3V SPI3 Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                   |  |

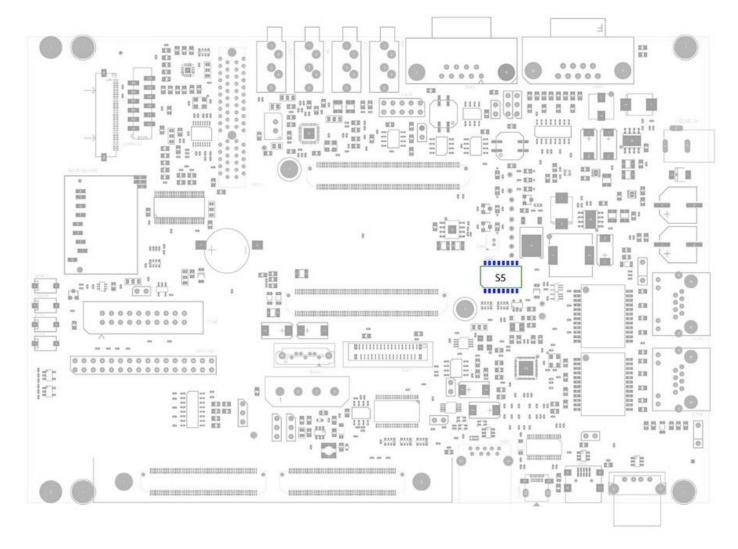

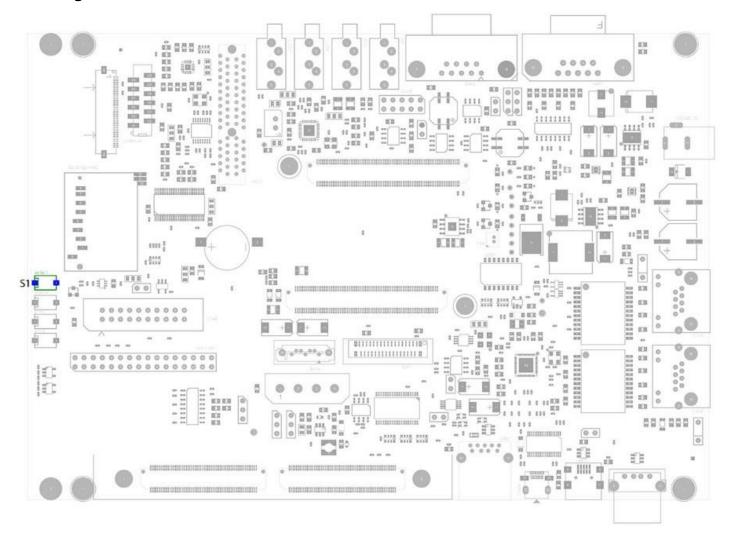

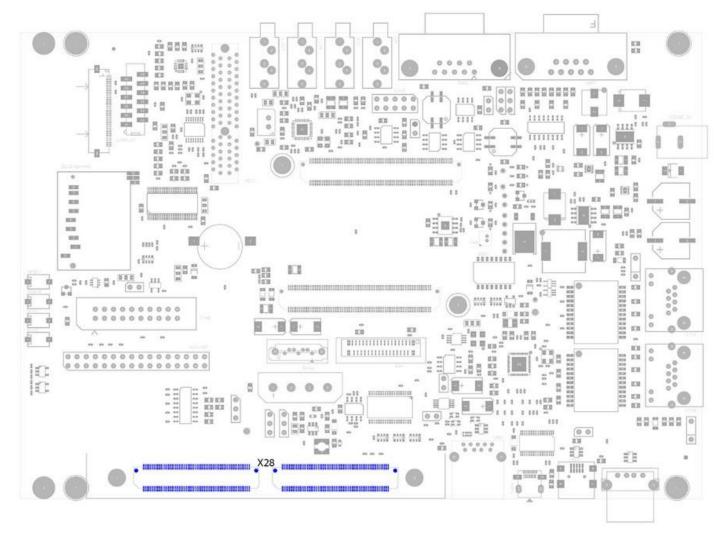

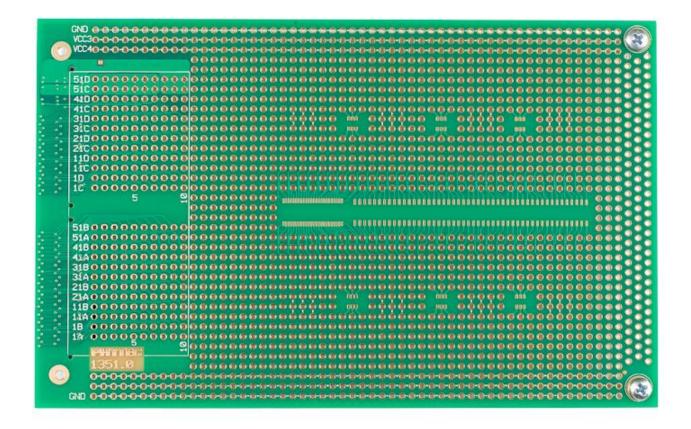

| B52 GND Ground 0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                   |  |