# phyCORE-AM3517

# **System on Module and Carrier Board**

# **Hardware Manual**

Document No: L-761e\_2 Product No: PCM-048/PCM-961 SOM PCB No: 1335.1 CB PCB No: 1336.1 Edition: March 21, 2012

A product of a PHYTEC Technology Holding Company

In this manual are descriptions for copyrighted products that are not explicitly indicated as such. The absence of the trademark ( $^{\text{IM}}$ ) and copyright ( $^{\text{C}}$ ) symbols does not imply that a product is not protected. Additionally, registered patents and trademarks are similarly not expressly indicated in this manual.

The information in this document has been carefully checked and is believed to be entirely reliable. However, PHYTEC America LLC assumes no responsibility for any inaccuracies. PHYTEC America LLC neither gives any guarantee nor accepts any liability whatsoever for consequential damages resulting from the use of this manual or its associated product. PHYTEC America LLC reserves the right to alter the information contained herein without prior notification and accepts no responsibility for any damages which might result.

Additionally, PHYTEC America LLC offers no guarantee nor accepts any liability for damages arising from the improper usage or improper installation of the hardware or software. PHYTEC America LLC further reserves the right to alter the layout and/or design of the hardware without prior notification and accepts no liability for doing so.

© Copyright 2011 PHYTEC America LLC, Bainbridge Island, WA.

Rights - including those of translation, reprint, broadcast, photomechanical or similar reproduction and storage or processing in computer systems, in whole or in part - are reserved. No reproduction may occur without the express written consent from PHYTEC America LLC.

|                       | EUROPE                                                                           | NORTH AMERICA                                                                              |

|-----------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| Address:              | PHYTEC Technologie Holding AG<br>Robert-Koch-Str. 39<br>D-55129 Mainz<br>GERMANY | PHYTEC America LLC<br>203 Parfitt Way SW, Suite G100<br>Bainbridge Island, WA 98110<br>USA |

| Ordering Information: | +49 (800) 0749832                                                                | 1 (800) 278-9913                                                                           |

| Technical Support:    | +49 (6131) 9221-31                                                               | 1 (800) 278-9913                                                                           |

| Fax:                  | +49 (6131) 9221-33                                                               | 1 (206) 780-9135                                                                           |

| Website:              | http://www.phytec.eu/europe                                                      | http://www.phytec.com                                                                      |

## **Table of Contents**

| List of Tables                                                                                                               | 188 |

|------------------------------------------------------------------------------------------------------------------------------|-----|

| List of Figures                                                                                                              | v   |

| Conventions, Abbreviations, and Acronymsvi                                                                                   |     |

| Part I: PCM-048/phyCORE-AM3517 System on Module                                                                              |     |

| 1.1 Block Diagram       1.1 Block Diagram         1.2 View of the phyCORE-AM3517                                             | 4   |

| 2 Pin Description                                                                                                            | 7   |

| <sup>.</sup> 3.1 Jumper Settings                                                                                             | 22  |

| 4.1 Primary System Power (VIN & VIN_3V3)       2         4.2 Secondary Battery Power (VBAT)       2                          |     |

| 4.3 PMIC Supplies (U2)       2         4.4 RTC Supplies (U2)       2                                                         |     |

| 4.5       Selecting Shunt Resistors for Current Measurements       2         4.6       Voltage Supervisor (U2, U21)       2  |     |

| 5 External RTC (U22)                                                                                                         | 29  |

| 6.1 Boot Process         3           7 System Memory         3                                                               | 33  |

| 7.1       SDRAM (U8, U9)                                                                                                     | 33  |

| 7.3 EEPROM (U13)                                                                                                             | 34  |

| 8 Serial Interfaces.         3           8.1 RS-232 Transceiver (U15).         3           8.2 Ethernet PHY (U12).         3 | 35  |

| 8.3 USB OTG (U1)                                                                                                             | 35  |

| 9 Debug Interface (X1)                                                                                                       | 37  |

| 11 General Purpose Memory Controller (U2).       3         12 LCD LVDS Transmitter       4                                   | 39  |

| 12.1 LVDS and SOM I/O Voltage (J23).       4         13 AM3517 IO and GPMC Bus Voltage       4                               | 11  |

| 14 Technical Specifications       4         15 Hints for Handling the phyCORE-AM3517       4                                 |     |

| Part II: PCM-961/phyCORE-AM3517 Carrier Board                                                                                | 16  |

| 16 Introduction       4         17 Overview of Peripherals       4         18 Jumpers       5                                | 18  |

| 19 phyCORE-AM3517 SOM Connectivity       5         20 Power       5                                                          | 55  |

| 20.1 Wall Adapter Input (X9)         5           20.2 Power over Ethernet (PoE)         5                                    | 56  |

|     | 20.3 Lithium-Ion Battery               | 58  |

|-----|----------------------------------------|-----|

|     | 20.4 3.3V Supply (U27)                 |     |

|     | 20.5 1.8V Supply (U31)                 |     |

|     | 20.6 Current Measurement               |     |

| 21  |                                        |     |

| 21  | JTAG Connectivity.                     |     |

|     | Audio Interface                        |     |

|     | Ethernet Connectivity                  |     |

|     | USB Connectivity.                      |     |

|     | LCD and DVI Connectivity.              |     |

|     | 25.1 DVI Connector                     |     |

|     | 25.2 LVDS Connectors                   |     |

|     | 25.3 TTL LCD Connector                 |     |

| 26  | GPIO Expansion Connector               |     |

|     | RS-232 Connectivity                    |     |

|     | SD/SDIO/MMC Connectivity               |     |

| 29  |                                        |     |

| -   | Wireless Connector                     |     |

|     | TV Out                                 |     |

|     | Camera Interface.                      |     |

|     | User Buttons                           |     |

|     | User LEDs                              |     |

| 35  |                                        |     |

|     | Boot Mode Selection                    |     |

|     | System Reset Button.                   |     |

| 00  |                                        | 02  |

| Pa  | rt III:                                | 93  |

|     |                                        | ••• |

| Par | rt III: PCM-988/GPIO Expansion Board   | 93  |

|     | Introduction                           |     |

|     | System Signal Mapping.                 |     |

|     | GPMC Signal Mapping                    |     |

|     | UART Signal Mapping.                   |     |

|     | I <sup>2</sup> C Signal Mapping        |     |

|     | GPIO Signal Mapping                    |     |

|     | USB Signal Mapping                     |     |

|     | CAN Signal Mapping                     |     |

|     | Ethernet Signal Mapping                |     |

|     | HDQ Signal Mapping.                    |     |

|     | McBSP Signal Mapping.                  |     |

|     | SPI Signal Mapping.                    |     |

|     | Power Signal Mapping.                  |     |

|     | ······································ |     |

| Rev | vision History                         | 109 |

# **List of Tables**

| Conventions, Abbreviations, and Acronyms                                                                                                                                                                        | .vi  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Table i-1. Abbreviations and Acronyms Used in This Manual                                                                                                                                                       | . vi |

|                                                                                                                                                                                                                 |      |

| Part I: PCM-048/phyCORE-AM3517 System on Module                                                                                                                                                                 |      |

| Table 2-1. Pin Descriptions, phyCORE-Connector X2, Row A                                                                                                                                                        |      |

| Table 2-2. Pin Descriptions, phyCORE-Connector X2, Row B                                                                                                                                                        |      |

| Table 2-3. Pin Descriptions, phyCORE-Connector X2, Row C                                                                                                                                                        |      |

| Table 2-4. Pin Descriptions, phyCORE-Connector X2, Row D                                                                                                                                                        |      |

| Table 3-1. Jumper Settings                                                                                                                                                                                      |      |

| Table 4-1. Current Measurements                                                                                                                                                                                 |      |

| Table 6-1. Peripheral Booting Configuration Pins after POR                                                                                                                                                      |      |

| Table 6-2. Booting Configuration Pins after a Warm Reset                                                                                                                                                        |      |

| Table 7-1. Valid SDRAM Memory Address Ranges                                                                                                                                                                    |      |

| Table 7-2. LOCK Pin Jumper Settings                                                                                                                                                                             |      |

| Table 7-3. phyCORE-AM3517 Memory Map    Map                                                                                                                                                                     |      |

| Table 8-1. UART3 TTL and RS-232 Level Signals                                                                                                                                                                   |      |

| Table 8-2. Applicable USB Operating Mode Connectors                                                                                                                                                             |      |

| Table 11-1. GPMC Signal Mapping                                                                                                                                                                                 |      |

| Table 14-1. Technical Specifications                                                                                                                                                                            |      |

| Table 14-2. Static Operating Characteristics                                                                                                                                                                    | 44   |

|                                                                                                                                                                                                                 |      |

| Part II: PCM-961/phyCORE-AM3517 Carrier Board                                                                                                                                                                   |      |

| Table 17-1. Connectors and Headers                                                                                                                                                                              |      |

| Table 17-2. Description of the Buttons and Switches                                                                                                                                                             |      |

| Table 17-3. Description of LEDs                                                                                                                                                                                 |      |

| Table 18-1. Jumper Settings         Table 20.4. Describes Ethernal DOE Options                                                                                                                                  |      |

| Table 20-1. Possible Ethernet PSE Options                                                                                                                                                                       |      |

| Table 21-1. phyCORE-AM3517 JTAG Connector X13 Pin Descriptions         Table 21-2. Operative JTAG Connector X13 Pin Descriptions                                                                                |      |

| Table 21-2. Compatible JTAG Probes for the phyCORE-AM3517 Carrier Board         Table 25-4       24-bit 2.0.0 minute (24-4.0.04 b)         Table 25-4       24-bit 2.0.0 minute (24-4.0.04 b)                   |      |

| Table 25-1. 24-bit 8:8:8 mode (S1-1,S1-2, S1-3, S1-4 = 0,0,0,0)                                                                                                                                                 |      |

| Table 25-2. 12-bit 4:4:4 mode (S1-1,S1-2, S1-3, S1-4 = C, C, C, O)                                                                                                                                              |      |

| Table 25-3. 16-bit 5:6:5 mode (S1-1,S1-2, S1-3, S1-4 = C, C, O, C)                                                                                                                                              |      |

| Table 25-4. 18-bit 6:6:6 mode (S1-1,S1-2, S1-3, S1-4 = C, C, O, O)                                                                                                                                              |      |

| Table 25-5. LCD Mode Jumper Summary (S1-1,S1-2, S1-3, S1-4)         Table 27.4. Compositor D1 (UADT2) Dia Descriptions                                                                                          |      |

| Table 27-1. Connector P1 (UART3) Pin Descriptions         Table 27-2. Connector V20 (UART3) Pin Descriptions                                                                                                    |      |

| Table 27-2. Connector X29 (UART2) Pin Descriptions         Table 27-2. The UART Discussion of the Uarder (X10) Descriptions                                                                                     |      |

| Table 27-3. TTL UART Pin Header (X10) Descriptions       Table 28-1. SDIO Easy Access Header Connector Signal Descriptions                                                                                      |      |

|                                                                                                                                                                                                                 |      |

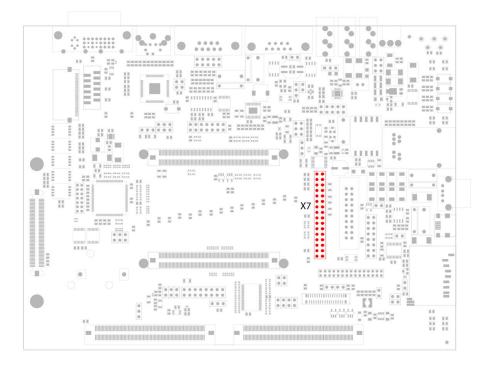

| Table 30-1. Wireless Connector (X7) Signal Descriptions         Table 32.1. Compare Interface (X4) Signal Descriptions                                                                                          |      |

| Table 32-1. Camera Interface (X4) Signal Descriptions         Table 35-1. Dest Selection Switches and Descriptions                                                                                              |      |

| Table 35-1. Boot Selection Switches and Descriptions       Table 35-2. Boot Order Switch Configurations         Table 35-2. Boot Order Switch Configurations       Table 35-2. Boot Order Switch Configurations |      |

|                                                                                                                                                                                                                 | 09   |

| Part III:                                                                                                                                                                                                       | as   |

|                                                                                                                                                                                                                 | 35   |

| Part III: PCM-988/GPIO Expansion Board                                                                                                                                                                          | 93   |

| Table 37-1. GPIO Expansion Connector - Signals Removed                                                                                                                                                          |      |

| Table 38-1. System Signal Mapping     System Signal Mapping                                                                                                                                                     |      |

| Table 39-1. GPMC Signal Mapping         Table 39-1. GPMC Signal Mapping                                                                                                                                         |      |

| Table 40-1. UART Signal Mapping         Table 40-1. UART Signal Mapping                                                                                                                                         |      |

| Table 41-1. I <sup>2</sup> C Signal Mapping   1                                                                                                                                                                 |      |

|                                                                                                                                                                                                                 | -    |

| Table 42-1. GPIO Signal Mapping    ···································· | 101 |

|-------------------------------------------------------------------------|-----|

| Table 43-1. USB Signal Mapping                                          | 102 |

| Table 44-1. CAN Signal Mapping    ····································  | 103 |

| Table 45-1. Ethernet Signal Mapping                                     | 104 |

| Table 46-1. HDQ Signal Mapping                                          | 105 |

| Table 47-1. McBSP Signal Mapping                                        | 106 |

| Table 48-1. SPI Signal Mapping    ····································  | 107 |

| Table 49-1. Power Signal Mapping                                        | 108 |

| Revision History                                                        | 109 |

| Table 50-1. Revision History    ····································    | 109 |

# **List of Figures**

| Part I: PCM-048/phyCORE-AM3517 System on Module                    | . 1 |

|--------------------------------------------------------------------|-----|

| Fig. 1-1. phyCORE-AM3517 Block Diagram                             | . 4 |

| Fig. 1-2. Top View of the phyCORE-AM3517 (Controller Side)         | . 5 |

| Fig. 1-3. Bottom View of the phyCORE-AM3517 (Connector Side)       | . 6 |

| Fig. 2-1. Pin-out of the phyCORE-Connector                         |     |

| (Top View, with Cross Section Insert)                              | . 8 |

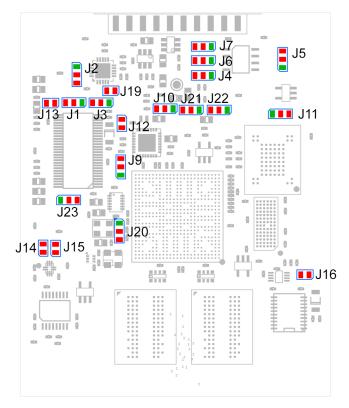

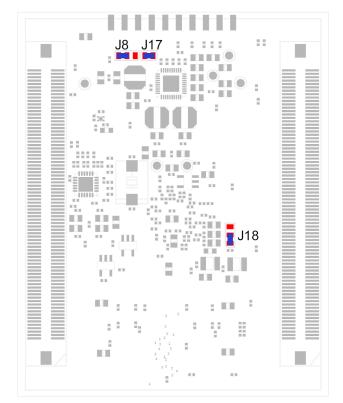

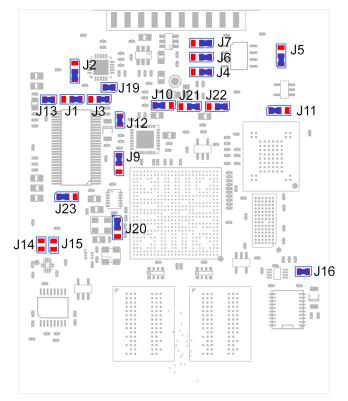

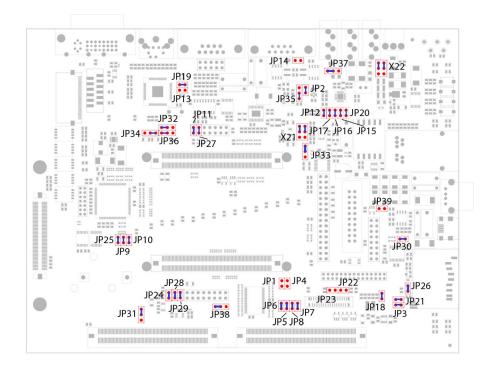

| Fig. 3-1. Jumper Locations (Connector Side).                       |     |

| Fig. 3-2. Jumper Locations (Controller Side)                       |     |

| Fig. 3-3. Default Jumper Settings (Connector Side).                |     |

| Fig. 3-4. Default Jumper Settings (Controller Side)                |     |

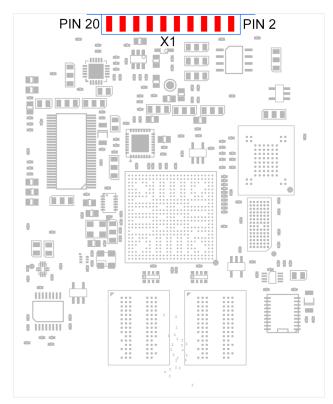

| Fig. 9-1. JTAG Interface X1 (Controller Side).                     |     |

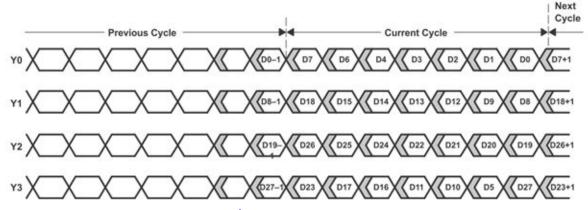

| Fig. 12-1. LVDS Multiplexing Scheme1                               |     |

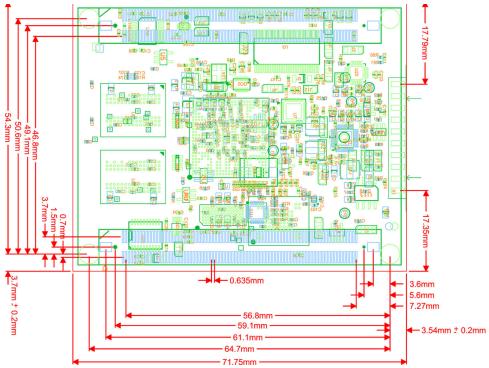

| Fig. 14-1. phyCORE-AM3517 Physical Dimensions                      |     |

|                                                                    | 43  |

| Part II: PCM-961/phyCORE-AM3517 Carrier Board                      | 46  |

| Fig. 16-1. phyCORE-AM3517 Carrier Board                            |     |

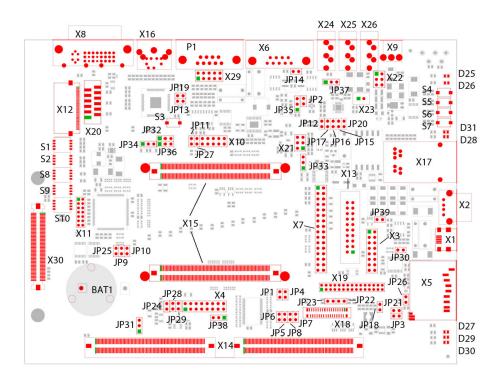

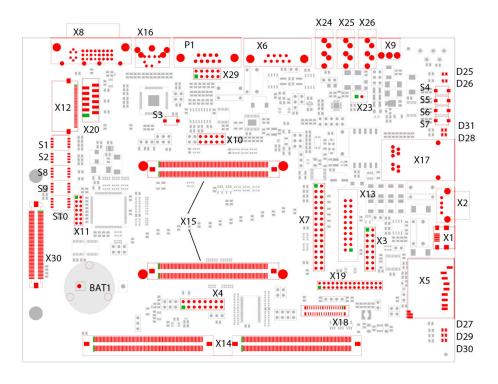

| Fig. 17-1. Overview of Peripherals                                 |     |

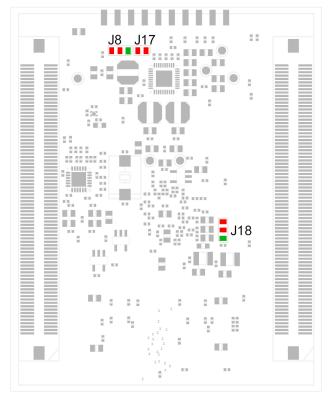

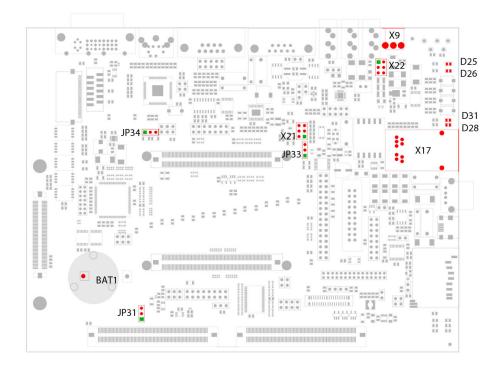

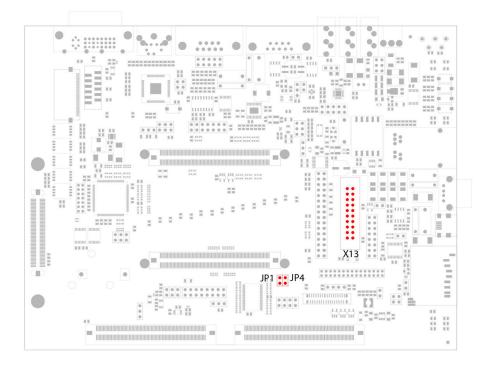

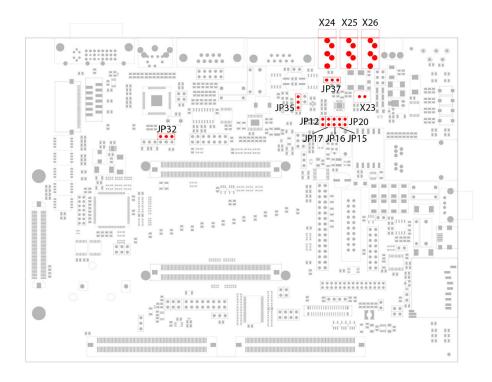

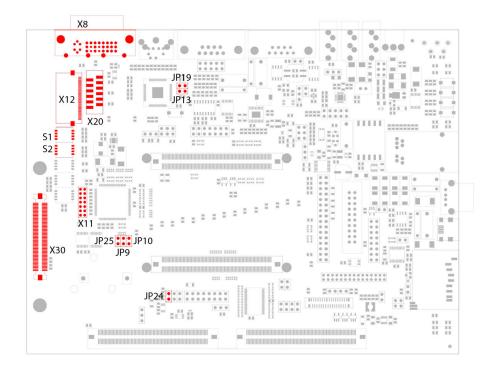

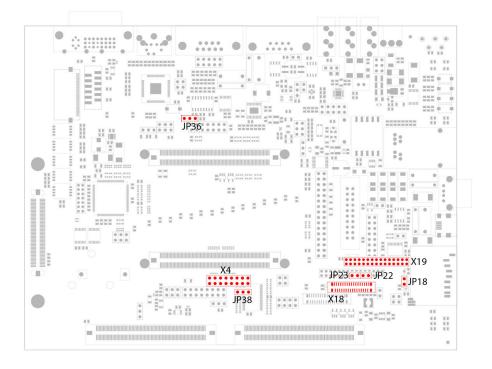

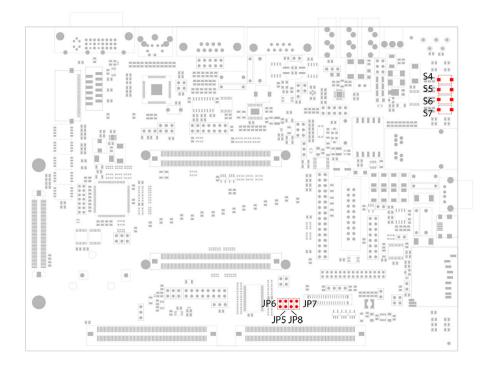

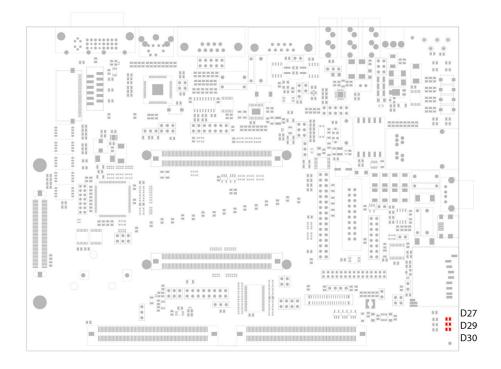

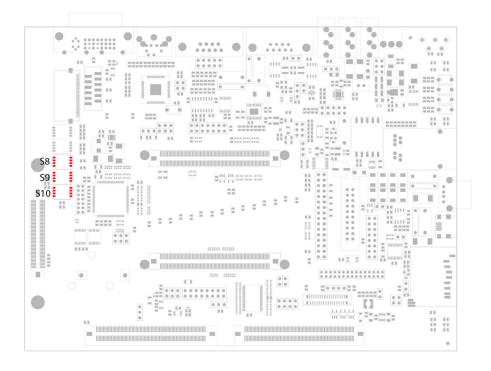

| Fig. 18-1. Jumper Locations and Default Settings                   |     |

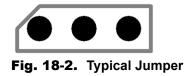

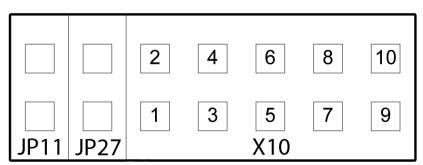

| Fig. 18-2. Typical Jumper Pad Numbering Scheme (Removable Jumpers) |     |

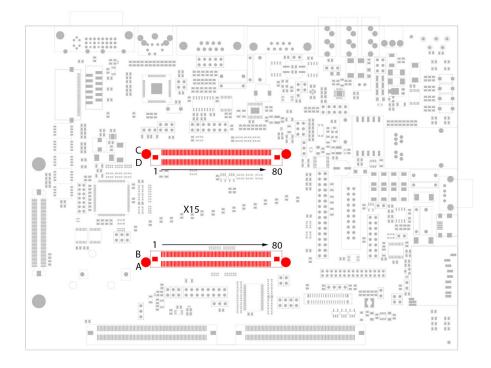

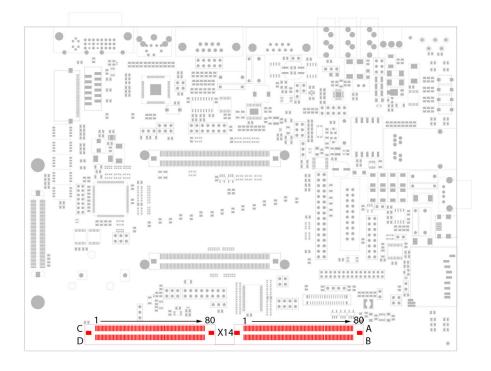

| Fig. 19-1. phyCORE-AM3517 SOM Connectivity to the Carrier Board    |     |

| Fig. 20-1. Powering Scheme                                         |     |

| Fig. 21-1. JTAG Probe Connectivity to the phyCORE-AM3517           |     |

|                                                                    |     |

| Fig. 22-1. Audio Interface Connectors and Jumpers                  |     |

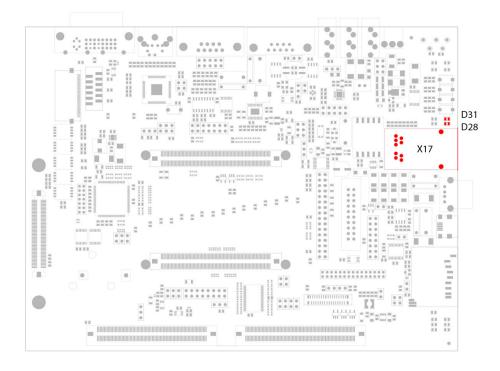

| Fig. 23-1. Ethernet Interface Connector and LEDs                   |     |

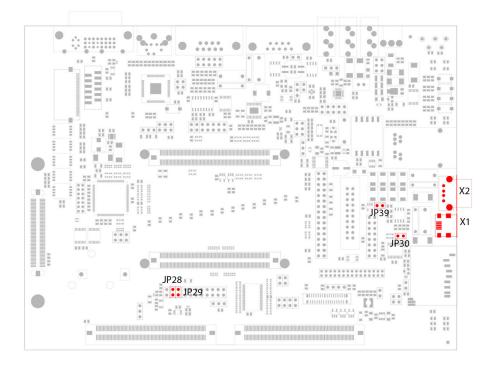

| Fig. 24-1. USB Interface Connectors and Jumpers                    |     |

| Fig. 25-1. LCD/DVI Interface Connectors, Jumpers, and Switches     |     |

| Fig. 25-2. LCD Signal Mapping in 24-bit Mode with a 24-bit LCD     |     |

| Fig. 25-3. LCD Signal Mapping in 16-bit Mode with an 16-Bit LCD    |     |

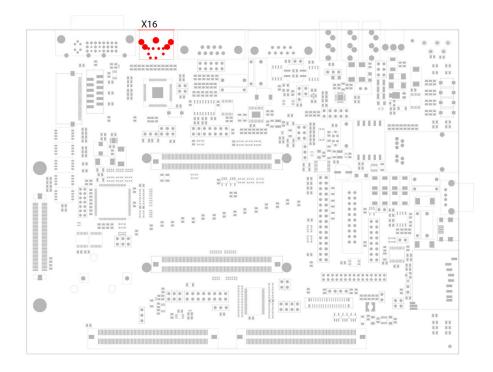

| Fig. 26-1. GPIO Expansion Connector                                |     |

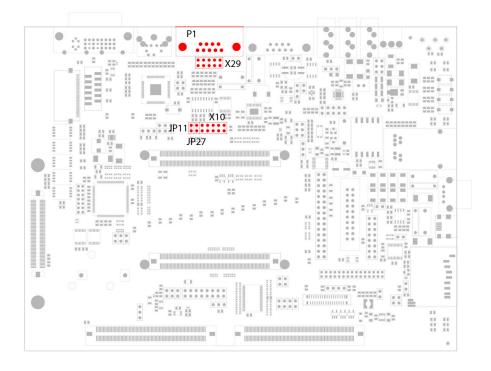

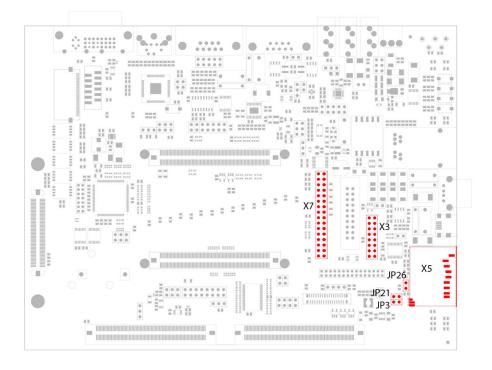

| Fig. 27-1. RS-232 Interface Connectors and Jumpers                 | 73  |

| Fig. 27-2. DB9 RS-232 Connectors P1 (UART3) Pin Numbering          | 73  |

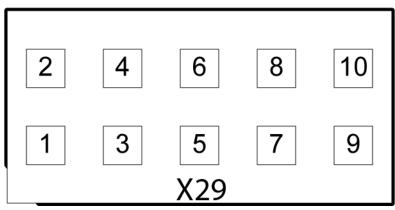

| Fig. 27-3. Connector X29 (UART2) Pin Numbering                     | 74  |

| Fig. 27-4. UART3/UART2 Header Connector X10 Pin Numbering          | 75  |

| Fig. 28-1. SDIO Interface Connectors and Jumpers                   | 77  |

| Fig. 29-1. CAN Interface Connectors and Jumpers                    |     |

| Fig. 30-1. Wireless Interface Connector                            |     |

| Fig. 31-1. TV Out Connector                                        |     |

| Fig. 32-1. Camera Interface Connectors and Jumpers                 |     |

| Fig. 33-1. User Buttons and Jumpers.                               |     |

| Fig. 34-1. User LEDs and Jumpers                                   |     |

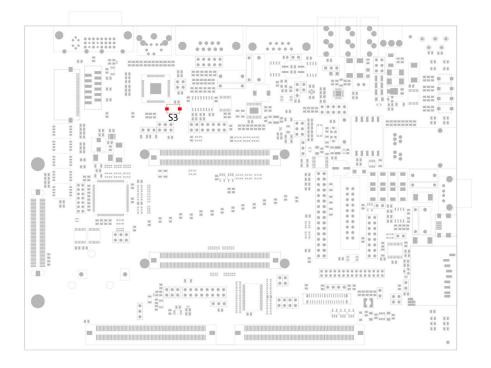

| Fig. 35-1. Boot Mode Selection Connectors and Jumpers              |     |

|                                                                    |     |

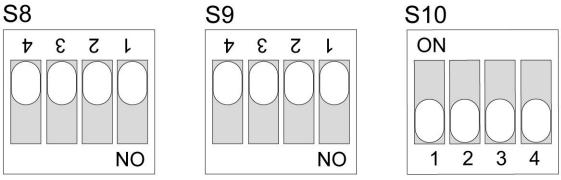

| Fig. 35-2. Boot Switches - Default Settings                        |     |

| Fig. 36-1. System Reset Button                                     | 92  |

| Part III:                                                          | 93  |

|                                                                    |     |

| Part III: PCM-988/GPIO Expansion Board                             |     |

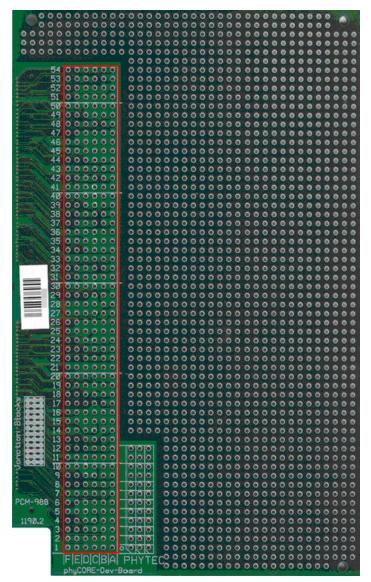

| Fig. 37-1. PCM-988/GPIO Expansion Board and Patch Field            | 94  |

### **Conventions, Abbreviations, and Acronyms**

#### Conventions

The conventions used in this manual are as follows:

- Signals that are preceded by a "/" character are designated as active low signals. Their active state is when they are driven low, or are driving low; for example: /RESET.

- Tables show the default setting or jumper position in **bold**, teal text.

- Text in blue indicates a hyperlink, either internal or external to the document. Click these links to quickly jump to the applicable URL, part, chapter, table, or figure.

- References made to the *phyCORE-Connector* always refer to the high density molex connectors on the underside of the phyCORE-AM3517 System on Module.

#### **Abbreviations and Acronyms**

Many acronyms and abbreviations are used throughout this manual. Use the table below to navigate unfamiliar terms used in this document.

| Abbreviation | Definition                                                                                                                                                    |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BTN1         | User button 1; used in reference to one of the four available user buttons on the Car-<br>rier Board                                                          |

| BTN2         | User button 2; used in reference to one of the four available user buttons on the Car-<br>rier Board                                                          |

| BTN3         | User button 3; used in reference to one of the four available user buttons on the Car-<br>rier Board                                                          |

| BTN4         | User button 4; used in reference to one of the four available user buttons on the Carrier Board                                                               |

| СВ           | Carrier Board; used in reference to the PCM-961/phyCORE-AM3517 Carrier Board                                                                                  |

| CPLD         | Complex Programmable Logic Device                                                                                                                             |

| EMI          | Electromagnetic Interference                                                                                                                                  |

| GPI          | General purpose input                                                                                                                                         |

| GPIO         | General purpose input and output                                                                                                                              |

| GPIOEBPF     | GPIO Expansion Board Patch Field; used in reference with the PCM-988/GPIO<br>Expansion Board and its associated patch field                                   |

| GPMC         | General Purpose Memory Controller                                                                                                                             |

| GPO          | General purpose output                                                                                                                                        |

| J            | Solder jumper; these types of jumpers require solder equipment to remove and place                                                                            |

| JP           | Solderless jumper; these types of jumpers can be removed and placed by hand with no special tools                                                             |

| PCB          | Printed circuit board                                                                                                                                         |

| PoE          | Power over Ethernet                                                                                                                                           |

| POT          | Potentiometer                                                                                                                                                 |

| PMIC         | Power Management Integrated Circuit                                                                                                                           |

| PSE          | Power sourcing equipment; the device in a PoE network that provides power to con-<br>nected devices - usually a switch, router, or stand alone power injector |

#### **Table i-1.** Abbreviations and Acronyms Used in This Manual

| Abbreviation | Definition                                                                            |  |

|--------------|---------------------------------------------------------------------------------------|--|

| RTC          | Real-time clock                                                                       |  |

| SMT          | Surface mount technology                                                              |  |

| SOM          | System on Module; used in reference to the PCM-048/phyCORE-AM3517 System<br>on Module |  |

| TRM          | Technical Reference Manual                                                            |  |

| VBAT         | SOM battery supply input                                                              |  |

| VFP          | Vector Floating Point                                                                 |  |

| Table i-1. A | Abbreviations and Acronym | ns Used in This Manual |

|--------------|---------------------------|------------------------|

|--------------|---------------------------|------------------------|

**F**

#### Preface

This phyCORE-AM3517 Hardware Manual describes the System on Module's design and functions. Precise specifications for the Texas Instruments AM3517 processor can be found in the processor datasheet and/or user's manual.

In this hardware manual and in the schematics, active low signals are denoted by a "/" preceding the signal name, for example: /RD. A "0" represents a logic-zero or low-level signal, while a "1" represents a logic-one or high-level signal.

# Declaration of Electro Magnetic Conformity of the PHYTEC phyCORE-AM3517

PHYTEC System on Modules (SOMs) are designed for installation in electrical appliances or, combined with the PHYTEC Carrier Board, can be used as dedicated Evaluation Boards (for use as a test and prototype platform for hardware/software development) in laboratory environments.

#### CAUTION:

PHYTEC products lacking protective enclosures are subject to damage by ESD and, hence, may only be unpacked, handled or operated in environments in which sufficient precautionary measures have been taken in respect to ESD-dangers. It is also necessary that only appropriately trained personnel (such as electricians, technicians and engineers) handle and/or operate these products. Moreover, PHYTEC products should not be operated without protection circuitry if connections to the product's pin header rows are longer than 3 m.

PHYTEC products fulfill the norms of the European Union's Directive for Electro Magnetic Conformity only in accordance to the descriptions and rules of usage indicated in this hardware manual (particularly in respect to the pin header row connectors, power connector and serial interface to a host-PC).

Implementation of PHYTEC products into target devices, as well as user modifications and extensions of PHYTEC products, is subject to renewed establishment of conformity to, and certification of, Electro Magnetic Directives. Users should ensure conformance following any modifications to the products as well as implementation of the products into target systems.

The phyCORE-AM3517 is one of a series of PHYTEC System on Modules that can be populated with different controllers and, hence, offers various functions and configurations. PHYTEC supports a variety of 8-/16- and 32-bit controllers in two ways:

- 1. As the basis for Rapid Development Kits which serve as a reference and evaluation platform.

- 2. As insert-ready, fully functional phyCORE OEM modules, which can be embedded directly into the user's peripheral hardware design.

Implementation of an OEM-able SOM subassembly as the "core" of your embedded design allows you to focus on hardware peripherals and firmware without expending resources to "re-invent" microcontroller circuitry. Furthermore, much of the value of the phyCORE module lies in its layout and test.

Production-ready Board Support Packages (BSPs) and Design Services for our hardware further reduce development time and expenses. Take advantage of PHYTEC products to shorten time-to-market, reduce development costs, and avoid substantial design issues and risks. For more information go to:

http://www.phytec.com/services/design-services/index.html

# Part I: PCM-048/phyCORE-AM3517 System on Module

Part 1 of this three part manual provides detailed information on the phyCORE-AM3517 System on Module (SOM) designed for custom integration into customer applications.

The information in the following chapters is applicable to the 1335.1 PCB revision of the phyCORE-AM3517 SOM.

#### **1** Introduction

The phyCORE-AM3517 belongs to PHYTEC's phyCORE System on Module (SOM) family. The phyCORE SOMs represent the continuous development of PHYTEC SOM technology. Like its mini-, micro-, and nanoMODUL predecessors, the phyCORE boards integrate all core elements of a microcontroller system on a subminiature board and are designed in a manner that ensures their easy expansion and embedding in peripheral hardware developments.

As independent research indicates that approximately 70% of all EMI (Electro Magnetic Interference) problems stem from insufficient supply voltage grounding of electronic components in high frequency environments, the phyCORE board design features an increased pin package. The increased pin package allows dedication of approximately 20% of all connector pins on the phyCORE boards to ground. This improves EMI and EMC characteristics and makes it easier to design complex applications meeting EMI and EMC guidelines using phyCORE boards even in high noise environments.

phyCORE boards achieve their small size through modern SMD technology and multi-layer design. In accordance with the complexity of the module, 0402-packaged SMD components and laser-drilled Microvias are used on the boards, providing phyCORE users with access to this cutting edge miniaturization technology for integration into their own design.

The phyCORE-AM3517 is a sub-miniature (72 x 58 mm) insert-ready SOM populated with Texas Instruments AM3517 ARM Cortex-A8 core processor. Its universal design enables its insertion into a wide range of embedded applications. All processor signals and ports extend from the processor to high-density pitch (0.635 mm) connectors aligning two sides of the board. This allows the SOM to be plugged like a "big chip" into a target application.

Precise specifications for the processor populating the board can be found in the applicable processor user's manual and datasheet. The descriptions in this manual are based on the Texas Instruments ARM Cortex A8/AM3517 processor. No description of compatible processor derivative functions is included, as such functions are not relevant for the basic functioning of the phyCORE-AM3517.

#### The phyCORE-AM3517 offers the following features:

- Insert-ready, sub-miniature (72 x 58 mm) System on Module (SOM) subassembly in low EMI design, achieved through advanced SMD technology

- Populated with the Texas Instruments AM3517 processor (491-ball BGA packaging)

- Improved interference safety achieved through multi-layer PCB technology and dedicated ground pins

- Controller signals and ports extend to two 160-pin high-density (0.635 mm) Molex connectors aligning two sides of the board, enabling it to be plugged like a "big chip" into target application

- Maximum 600 MHz core clock frequency

- NEON (TM) SIMD co-processor and Vector Floating Point (VFP) co-processor

- 16KB instruction cache (4-way set-associative)

- 16KB data cache (4-way set-associative)

- 256KB L2 cache

- System direct memory access (sDMA) controller (32 logical channels with configurable priority)

- Memory Management Unit (MMU)

- 32-bit DDR2-333MHz, 256 or 512MByte SDRAM running at 1.8V

- General Purpose Memory Controller supporting 16-bit wide multiplexed address/data bus

- 12 32-bit General Purpose Timers

- 64 KB SRAM

- 128, 256, or 512 MB of on-board NAND flash at 1.8V (bootable)

- HD resolution display subsystem:

- Parallel Digital Output

- Up to 24-Bit RGB

- Supports up to two LCD Panels

- Support for Remote Frame Buffer Interface (RFBI) LCD Panels supporting

- Two 10-bit Digital-to-Analog Converters (DACs) supporting Composite NTSC/PAL Video and Luma/Chroma Separate Video (S-Video)

- Rotation 90, 180, and 270 degrees; image resizing from 1/4x to 8x

- Color Space Converter

- 8-bit Alpha Blending

- Video Processing Front End (VPFE) 16-bit video input port:

- RAW data interface

- 75-MHz maximum pixel clock

- Supports REC656/CCIR656 standard chip

- Supports YCbCr422 format (8-bit or 16-bit with discrete horizontal and vertical sync signals)

- Generates optical black clamping signals

- Built-in digital clamping and black level compensation

- 10-bit to 8-bit A-law compression hardware

- Up to 16K Pixels (Image Size) in horizontal and vertical directions

- 10/100 Mbit Ethernet (MAC and PHY)

- Multiport USB Host Subsystem [HS/FS/LS] DP/DM interface

- USB OTG transceiver for embedded USB host/peripheral functionality

- High-End CAN Controller (HECC)

- Six rail voltage supervision PMIC with programmable processor core voltage support and RTC priority voltage switch

- One 32-bit Watchdog Timer (internal to AM3517)

- Support for RealView ICE debug through standard JTAG interface

- Four Master/Slave Multichannel Serial Port Interface (McSPI) ports

- Five Multichannel Buffered Serial Ports: one 5K-Byte Transmit/Receive Buffer (McBSP2) and four 512-Byte transmit/receive buffers (McBSP1/3/4/5)

- Three Master/Slave high-speed Inter-Integrated circuit (I<sup>2</sup>C) controllers

- Two I<sup>2</sup>C ports

- 10/100 Ethernet with HP Auto MDIX support

- 24-bit LCD controller supporting STN and TFT panels at up to 1024x768 display resolution at 60Hz and 2048x2048 resolution at lower frame rates (PCLK max 75MHz).

- Touch screen controller

- Three removable media interfaces [MMC/SD/SDIO]

- Real-time clock (RTC) with dedicated interrupt (alarm clock function) and processor independent RTC consuming less than 275nA at 3.0V typical

- · Boot from NAND, USB, MMC/SDIO, Ethernet, and more

- JTAG interface for debugging and download of user code

- Up to 186 General-Purpose I/O (GPIO) pins

- Configurable IO voltage of 1.8V or 3.3V

- Single input supply voltage of 3.3 to 5.0V

- Industrial temperature range (-40C to +85C)

# 1.1 Block Diagram

| MAIN<br>CONNECTOR        |                  | AM3517                          |               | OPTIONAL<br>CONNECTOR    |

|--------------------------|------------------|---------------------------------|---------------|--------------------------|

| Power 1.8V/VCC IO        | PMIC             | Power UART1                     | RTS/CTS       | UART1 (RTS/CTS)          |

| HS USB HOST              | USB PHY          | USB HOST 4                      |               | USB HOST                 |

| HS USB OTG               | •                | USB OTG GPMC                    |               | Address/Data             |

| Ethernet                 | ETH PHY          | Ethernet                        | Shifters HAND |                          |

| UART3                    | RS-232           | UART3 SDRC                      | DDR2<br>SDRAM |                          |

| UART2                    | -Rx/Tx/RTS/CTS   | UART2 ETK                       | < <u> </u>    | ETK                      |

| UART1                    | •Rx/Tx•          | UART1 CCDC                      |               | CCDC                     |

| mcSPI (x1)               | •                | mcSPI (x1) ETH RMII             | <b>د</b>      | ETH RMII                 |

| mcBSP (x2)               | <b>ح</b>         | mcBSP (x2) MMC/SDIO (x1)        | <b>ح</b>      | MMC/SDIO (x1)            |

| CAN                      | •                | CAN mcBSP (x2)                  | <b>ح</b>      | mcBSP (x2)               |

| MMC/SDIO (x1)            | •                | MMC/SDIO (x1) mcSPI (x1)        | •             | mcSPI (x1)               |

| SYSTEM                   | •                | SYSTEM HS I <sup>2</sup> C (x1) | <b>د</b>      | HS I <sup>2</sup> C (x1) |

| HS I <sup>2</sup> C (x2) | EEPROM           | HS I <sup>2</sup> C (x2) JTAG   | ←             | JTAG                     |

|                          | RTC              | TV_OUT                          |               | TV_OUT                   |

| Touch                    | Touch Controller |                                 |               |                          |

| LVDS                     | LVDS             | LCD                             |               |                          |

| LCD                      | •                | On a wind                       |               |                          |

| One wire                 | <b>,</b>         | One wire                        |               |                          |

Fig. 1-1. phyCORE-AM3517 Block Diagram

#### 1.2 View of the phyCORE-AM3517

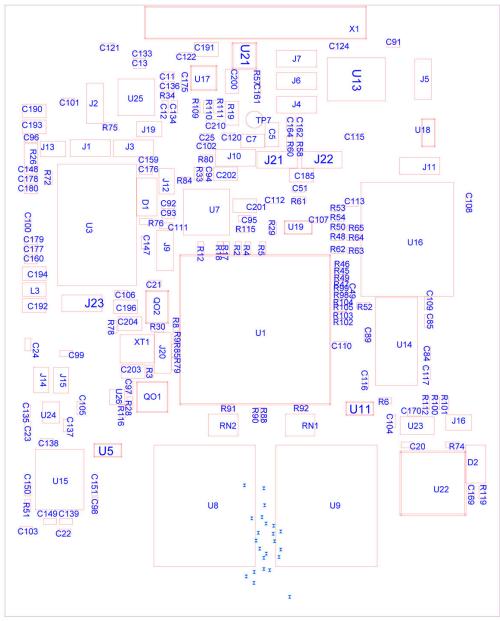

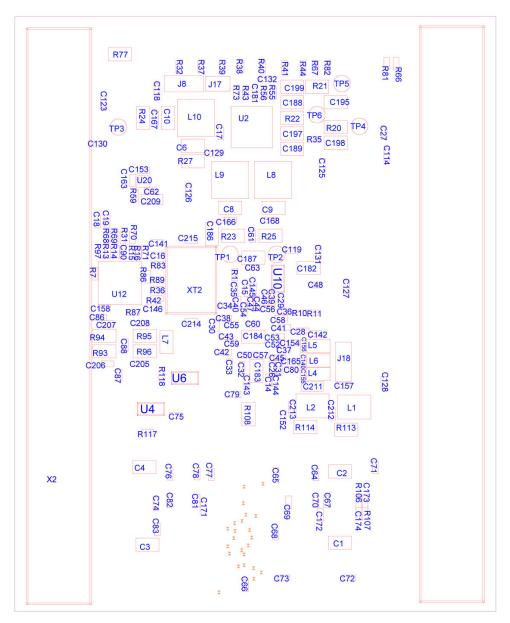

Fig. 1-2. Top View of the phyCORE-AM3517 (Controller Side)

Fig. 1-3. Bottom View of the phyCORE-AM3517 (Connector Side)

### 2 Pin Description

Please note that all module connections are not to exceed their expressed maximum voltage or current. Maximum signal input values are indicated in the corresponding controller manuals/datasheets. As damage from improper connections varies according to use and application, it is the user's responsibility to take appropriate safety measures to ensure that the module connections are protected from overloading through connected peripherals.

All controller signals extend to surface mount technology (SMT) connectors (0.635 mm) lining two sides of the module (referred to as the phyCORE-Connector). This allows the phyCORE-AM3517 to be plugged into any target application like a "big chip."

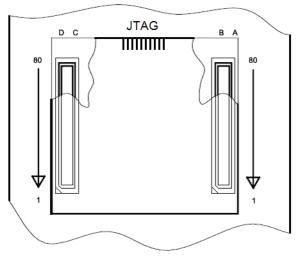

The numbering scheme for the phyCORE-Connector is based on a two dimensional matrix in which column positions are identified by a letter and row position by a number. Pin 1A, for example, is always located in the upper left hand corner of the matrix. The pin numbering values increase moving down on the board. Lettering of the pin connector rows progresses alphabetically from left to right (refer to Figure 2-1).

The numbered matrix can be aligned with the phyCORE-AM3517 (viewed from above; phyCORE-Connector pointing down) or with the socket of the corresponding phyCORE Carrier Board/user target circuitry. The upper left-hand corner of the numbered matrix (pin 1A) is thus covered with the corner of the phyCORE-AM3517 marked with a number 1. The numbering scheme is always in relation to the PCB as viewed from above, even if all connector contacts extend to the bottom of the module.

The numbering scheme is thus consistent for both the module's phyCORE-Connector as well as mating connectors on the phyCORE Carrier Board or target hardware, thereby considerably reducing the risk of pin identification errors.

Since the pins are exactly defined according to the numbered matrix previously described, the phyCORE-Connector is usually assigned a single designator for its position (X2 for example). In this manner the phyCORE-Connector comprises a single, logical unit regardless of the fact that it could consist of more than one physical socketed connector. The location of row 1 on the board is marked by a number 1 on the PCB to allow easy identification.

Figure 2-1 illustrates the numbered matrix system. It shows a phyCORE-AM3517 with SMT phyCORE-Connectors on its underside (defined as dotted lines) mounted on a Carrier Board. In order to facilitate understanding of the pin assignment scheme, the diagram presents a cross-view of the phyCORE module showing these phyCORE-Connectors mounted on the underside of the module's PCB.

**Fig. 2-1.** Pin-out of the phyCORE-Connector (Top View, with Cross Section Insert)

| Table 2-1. | Pin Descriptions | , phyCORE-Connector X2, Row A |

|------------|------------------|-------------------------------|

|------------|------------------|-------------------------------|

| Pin | Signal        | I/O | Signal<br>Level | Description                                         |

|-----|---------------|-----|-----------------|-----------------------------------------------------|

| 1A  | GPMC_NCS7     | 0   | VDDSHV          | GPMC interface - control (active low chip select 7) |

| 2A  | GND           | -   | -               | Ground                                              |

| 3A  | GPMC_NCS3     | 0   | VDDSHV          | GPMC interface - control (active low chip select 3) |

| 4A  | GPMC_NCS2     | 0   | VDDSHV          | GPMC interface - control (active low chip select 2) |

| 5A  | GPMC_NCS1     | 0   | VDDSHV          | GPMC interface - control (active low chip select 1) |

| 6A  | xGPMC_NWE     | 0   | VDDSHV          | GPMC interface - control (active low write enable)  |

| 7A  | GND           | -   | -               | Ground                                              |

| 8A  | GPMC_NBE0_CLE | 0   | VDDSHV          | GPMC interface - control (active low bus enable 0)  |

| 9A  | GPMC_NBE1     | 0   | VDDSHV          | GPMC interface - control (active low bus enable 1)  |

| 10A | GPMC_WAIT0    | I   | VDDSHV          | GPMC interface - control (active low wait signal)   |

| 11A | GPMC_WAIT2    | I   | VDDSHV          | GPMC interface - control (active low wait signal)   |

| 12A | GND           | -   | -               | Ground                                              |

| 13A | GPMC_A9       | 0   | VDDSHV          | GPMC interface - address                            |

| 14A | GPMC_A8       | 0   | VDDSHV          | GPMC interface - address                            |

| 15A | GPMC_A7       | 0   | VDDSHV          | GPMC interface - address                            |

| 16A | GPMC_A4       | 0   | VDDSHV          | GPMC interface - address                            |

| 17A | GND           | -   | -               | Ground                                              |

| 18A | GPMC_A1       | 0   | VDDSHV          | GPMC interface - address                            |

| 19A | GPMC_D15      | I   | VDDSHV          | GPMC interface - data                               |

| 20A | GPMC_D14      |     | VDDSHV          | GPMC interface - data                               |

| 21A | GPMC_D11      | I   | VDDSHV          | GPMC interface - data                               |

| 22A | GND           | -   | -               | Ground                                              |

|     |               |     |                 |                                                     |

### Table 2-1. Pin Descriptions, phyCORE-Connector X2, Row A (Continued)

| Pin | Signal         | I/O | Signal<br>Level | Description                                                                 |  |

|-----|----------------|-----|-----------------|-----------------------------------------------------------------------------|--|

| 23A | GPMC_D8        | I   | VDDSHV          | GPMC interface - data                                                       |  |

| 24A | GPMC_D7        | I   | VDDSHV          | GPMC interface - data                                                       |  |

| 25A | GPMC_D6        | I   | VDDSHV          | GPMC interface - data                                                       |  |

| 26A | GPMC_D3        | I   | VDDSHV          | GPMC interface - data                                                       |  |

| 27A | GND            | -   | -               | Ground                                                                      |  |

| 28A | GPMC_D0        | I   | VDDSHV          | GPMC interface - data                                                       |  |

| 29A | CCDC_WEN       | I   | VDDSHV          | CCD Camera interface - control (write enable)                               |  |

| 30A | CCDC_VD        | 10  | VDDSHV          | CCD Camera interface - control (vertical sync)                              |  |

| 31A | CCDC_FIELD     | 10  | VDDSHV          | CCD Camera interface - control (field identifica-<br>tion)                  |  |

| 32A | GND            | -   | -               | Ground                                                                      |  |

| 33A | CCDC_DATA5     | I   | VDDSHV          | CCD Camera interface - data                                                 |  |

| 34A | CCDC_DATA4     | I   | VDDSHV          | CCD Camera interface - data                                                 |  |

| 35A | CCDC_DATA3     | I   | VDDSHV          | CCD Camera interface - data                                                 |  |

| 36A | CCDC_DATA0     | I   | VDDSHV          | CCD Camera interface - data                                                 |  |

| 37A | GND            | -   | -               | Ground                                                                      |  |

| 38A | RMII_MDIO_CLK  | 0   | VDDSHV          | Ethernet - MDIO interface clock                                             |  |

| 39A | RMII_MDIO_DATA | IO  | VDDSHV          | Ethernet - MDIO interface data                                              |  |

| 40A | RMII_RXD1      | I   | VDDSHV          | Ethernet MAC - RMII data RX data                                            |  |

| 41A | RMII_RXER      | I   | VDDSHV          | Ethernet MAC - RMII data RX error                                           |  |

| 42A | GND            | -   | -               | Ground                                                                      |  |

| 43A | ETK_D15        | 0   | VDDSHV          | ARM Embedded Toolkit debug interface (other sig-<br>nal on HSUSB interface) |  |

| 44A | ETK_D14        | 0   | VDDSHV          | ARM Embedded Toolkit debug interface (other signal on HSUSB interface)      |  |

| 45A | ETK_D13        | 0   | VDDSHV          | ARM Embedded Toolkit debug interface (other signal on HSUSB interface)      |  |

| 46A | ETK_D10        | 0   | VDDSHV          | ARM Embedded Toolkit debug interface (other sig-<br>nal on HSUSB interface) |  |

| 47A | GND            | -   | -               | Ground                                                                      |  |

| 48A | HSUSB1_DATA3   | 10  | VDDSHV          | High Speed USB digital interface - data                                     |  |

| 49A | HSUSB1_DATA6   | 10  | VDDSHV          | High Speed USB digital interface - data                                     |  |

| 50A | HSUSB1_DATA5   | 10  | VDDSHV          | High Speed USB digital interface - data                                     |  |

| 51A | HSUSB1_DATA2   | 10  | VDDSHV          | High Speed USB digital interface - data                                     |  |

| 52A | GND            | -   | -               | Ground                                                                      |  |

| 53A | HSUSB1_STP     | 0   | VDDSHV          | High Speed USB digital interface - control                                  |  |

| 54A | xHSUSB1_CLK    | 0   | VDDSHV          | High speed USB digital interface 1 - clock                                  |  |

| 55A | MMC2_DAT7      | IO  | VDDSHV          | MMC / SDIO 2 interface - data                                               |  |

| 56A | MMC2_DAT4      | 10  | VDDSHV          | MMC / SDIO 2 interface - data                                               |  |

#### Table 2-1. Pin Descriptions, phyCORE-Connector X2, Row A (Continued)

| Pin | Signal      | I/O | Signal<br>Level                      | Description                                                                 |

|-----|-------------|-----|--------------------------------------|-----------------------------------------------------------------------------|

| 57A | GND         | -   | -                                    | Ground                                                                      |

| 58A | MMC2_DAT1   | 10  | VDDSHV                               | MMC / SDIO 2 interface - data                                               |

| 59A | MMC2_DAT0   | 10  | VDDSHV MMC / SDIO 2 interface - data |                                                                             |

| 60A | MMC2_CMD    | 0   | VDDSHV                               | MMC / SDIO 2 interface - command                                            |

| 61A | MCSPI2_CS1  | 0   | VDDSHV                               | Multichannel Serial Peripheral Interface 2 - chip select 1                  |

| 62A | GND         | -   | -                                    | Ground                                                                      |

| 63A | MCSPI2_CS0  | IO  | VDDSHV                               | Multichannel Serial Peripheral Interface 2 - chip select 0                  |

| 64A | MCSPI2_SIMO | IO  | VDDSHV                               | Multichannel Serial Peripheral Interface 2 - slave data in, master data out |

| 65A | MCSPI2_SOMI | 10  | VDDSHV                               | Multichannel Serial Peripheral Interface 2 - slave data out, master data in |

| 66A | xMCSPI2_CLK | 10  | VDDSHV                               | Multichannel Buffered Serial Port 2 - clock                                 |

| 67A | GND         | -   | -                                    | Ground                                                                      |

| 68A | TV_OUT1     | 0   | Analog                               | TV Out signal 1                                                             |

| 69A | TV_OUT2     | 0   | Analog                               | TV Out signal 2                                                             |

| 70A | MCBSP4_CLKX | 10  | VDDSHV                               | Multichannel Buffered Serial Port 4 - TX clock                              |

| 71A | MCBSP4_DR   | Ι   | VDDSHV                               | Multichannel Buffered Serial Port 4 - data receive                          |

| 72A | GND         | -   | -                                    | Ground                                                                      |

| 73A | MCBSP4_DX   | 10  | VDDSHV                               | Multichannel Buffered Serial Port 4 - data transmit                         |

| 74A | MCBSP4_FSX  | IO  | VDDSHV                               | Multichannel Buffered Serial Port 4 - frame sync<br>transmit                |

| 75A | N/C         | -   | -                                    | No connect                                                                  |

| 76A | JTAG_EMU0   | 10  | VDDSHV                               | JTAG - test emulation                                                       |

| 77A | GND         | -   | -                                    | Ground                                                                      |

| 78A | JTAG_NTRST  | I   | VDDSHV                               | JTAG - test reset                                                           |

| 79A | JTAG_TDI    | Ι   | VDDSHV                               | JTAG - test data in                                                         |

| 80A | xJTAG_TDO   | 0   | VDDSHV                               | JTAG - test data out                                                        |

#### Table 2-2. Pin Descriptions, phyCORE-Connector X2, Row B

| Pin | Signal    | I/O | Signal<br>Level | Description              |

|-----|-----------|-----|-----------------|--------------------------|

| 1B  | GPMC_NCS6 | 0   | VDDSHV          | GPMC interface - control |

| 2B  | GPMC_NCS5 | 0   | VDDSHV          | GPMC interface - control |

| 3B  | GPMC_NCS4 | 0   | VDDSHV          | GPMC interface - control |

| 4B  | GND       | -   | -               | Ground                   |

| 5B  | N/C       | -   | -               | No connect               |

### Table 2-2. Pin Descriptions, phyCORE-Connector X2, Row B (Continued)

| Pin | Signal         | I/O | Signal<br>Level | Description                                         |  |

|-----|----------------|-----|-----------------|-----------------------------------------------------|--|

| 6B  | GPMC_NWP       | 0   | VDDSHV          | GPMC interface - control (active low write protect) |  |

| 7B  | GPMC_NOE       | 0   | VDDSHV          | GPMC interface - control (active low output enable) |  |

| 8B  | xGPMC_NADV_ALE | 0   | VDDSHV          | GPMC interface - control                            |  |

| 9B  | GND            | -   | -               | Ground                                              |  |

| 10B | GPMC_WAIT1     |     | VDDSHV          | GPMC interface - control (active low wait)          |  |

| 11B | GPMC_WAIT3     |     | VDDSHV          | GPMC interface - control (active low wait)          |  |

| 12B | xGPMC_CLK      | 0   | VDDSHV          | GPMC interface - clock                              |  |

| 13B | GPMC_A10       | 0   | VDDSHV          | GPMC interface - address                            |  |

| 14B | GND            | -   | -               | Ground                                              |  |

| 15B | GPMC_A6        | 0   | VDDSHV          | GPMC interface - address                            |  |

| 16B | GPMC_A5        | 0   | VDDSHV          | GPMC interface - address                            |  |

| 17B | GPMC_A3        | 0   | VDDSHV          | GPMC interface - address                            |  |

| 18B | GPMC_A2        | 0   | VDDSHV          | GPMC interface - address                            |  |

| 19B | GND            | -   | -               | Ground                                              |  |

| 20B | GPMC_D13       | Ι   | VDDSHV          | GPMC interface - data                               |  |

| 21B | GPMC_D12       | Ι   | VDDSHV          | GPMC interface - data                               |  |

| 22B | GPMC_D10       | I   | VDDSHV          | GPMC interface - data                               |  |

| 23B | GPMC_D9        | Ι   | VDDSHV          | GPMC interface - data                               |  |

| 24B | GND            | -   | -               | Ground                                              |  |

| 25B | GPMC_D5        | Ι   | VDDSHV          | GPMC interface - data                               |  |

| 26B | GPMC_D4        | Ι   | VDDSHV          | GPMC interface - data                               |  |

| 27B | GPMC_D2        | I   | VDDSHV          | GPMC interface - data                               |  |

| 28B | GPMC_D1        | Ι   | VDDSHV          | GPMC interface - data                               |  |

| 29B | GND            | -   | -               | Ground                                              |  |

| 30B | CCDC_PCLK      | IO  | VDDSHV          | CCD Camera interface - control (pixel clock)        |  |

| 31B | CCDC_HD        | IO  | VDDSHV          | CCD Camera interface - control (horizontal sync)    |  |

| 32B | CCDC_DATA7     | I   | VDDSHV          | CCD Camera interface - data                         |  |

| 33B | CCDC_DATA6     | I   | VDDSHV          | CCD Camera interface - data                         |  |

| 34B | GND            | -   | -               | Ground                                              |  |

| 35B | CCDC_DATA2     |     | VDDSHV          | CCD Camera interface - data                         |  |

| 36B | CCDC_DATA1     | I   | VDDSHV          | CCD Camera interface - data                         |  |

| 37B | RMII_50MHZ_CLK | Ι   | VDDSHV          | Ethernet MAC - RMII clock                           |  |

| 38B | RMII_CRS_DV    | Ι   | VDDSHV          | Ethernet MAC - RMII data valid                      |  |

| 39B | GND            | -   | -               | Ground                                              |  |

| 40B | RMII_RXD0      | I   | VDDSHV          | Ethernet MAC - RMII data RX data                    |  |

| 41B | <br>RMII_TXD1  | 0   | VDDSHV          | Ethernet MAC - RMII data TX data                    |  |

| 42B | <br>RMII_TXD0  | 0   | VDDSHV          | Ethernet MAC - RMII data TX data                    |  |

| 43B | <br>RMII_TXEN  | 0   | VDDSHV          | Ethernet MAC - RMII data TX enable                  |  |

### Table 2-2. Pin Descriptions, phyCORE-Connector X2, Row B (Continued)

| Pin | Signal       | I/O | Signal<br>Level | Description                                                            |  |

|-----|--------------|-----|-----------------|------------------------------------------------------------------------|--|

| 44B | GND          | -   | -               | Ground                                                                 |  |

| 45B | ETK_D12      | 0   | VDDSHV          | ARM Embedded Toolkit debug interface (other sign on HSUSB interface)   |  |

| 46B | ETK_D11      | 0   | VDDSHV          | ARM Embedded Toolkit debug interface (other signal on HSUSB interface) |  |

| 47B | HSUSB1_NXT   | I   | VDDSHV          | High Speed USB digital interface - control                             |  |

| 48B | HSUSB1_DIR   | I   | VDDSHV          | High Speed USB digital interface - control                             |  |

| 49B | GND          | -   | -               | Ground                                                                 |  |

| 50B | HSUSB1_DATA4 | IO  | VDDSHV          | High Speed USB digital interface - data                                |  |

| 51B | HSUSB1_DATA7 | IO  | VDDSHV          | High Speed USB digital interface - data                                |  |

| 52B | HSUSB1_DATA1 | IO  | VDDSHV          | High Speed USB digital interface - data                                |  |

| 53B | HSUSB1_DATA0 | IO  | VDDSHV          | High Speed USB digital interface - data                                |  |

| 54B | GND          | -   | -               | Ground                                                                 |  |

| 55B | MMC2_DAT6    | IO  | VDDSHV          | MMC / SDIO 2 interface - data                                          |  |

| 56B | MMC2_DAT5    | IO  | VDDSHV          | MMC / SDIO 2 interface - data                                          |  |

| 57B | MMC2_DAT3    | IO  | VDDSHV          | MMC / SDIO 2 interface - data                                          |  |

| 58B | MMC2_DAT2    | IO  | VDDSHV          | MMC / SDIO 2 interface - data                                          |  |

| 59B | GND          | -   | -               | Ground                                                                 |  |

| 60B | xMMC2_CLK    | 0   | VDDSHV          | MMC / SDIO 2 interface - clock                                         |  |

| 61B | I2C3_SCL     | 0   | VDDSHV          | I <sup>2</sup> C bus 3 clock                                           |  |

| 62B | I2C3_SDA     | IO  | VDDSHV          | I <sup>2</sup> C bus 3 data                                            |  |

| 63B | UART1_RTS    | 0   | VDDSHV          | UART 1 ready to send                                                   |  |

| 64B | GND          | -   | -               | Ground                                                                 |  |

| 65B | UART1_CTS    | I   | VDDSHV          | UART 1 clear to send                                                   |  |

| 66B | N/C          | -   | -               | No connect                                                             |  |

| 67B | N/C          | -   | -               | No connect                                                             |  |

| 68B | N/C          | -   | -               | No connect                                                             |  |

| 69B | GND          | -   | -               | Ground                                                                 |  |

| 70B | MCBSP3_CLKX  | IO  | VDDSHV          | Multichannel Buffered Serial Port 3 - TX clock                         |  |

| 71B | MCBSP3_DR    | Ι   | VDDSHV          | Multichannel Buffered Serial Port 3 - data receive                     |  |

| 72B | MCBSP3_DX    | Ю   | VDDSHV          | Multichannel Buffered Serial Port 3 - data transmit                    |  |

| 73B | MCBSP3_FSX   | 10  | VDDSHV          | Multichannel Buffered Serial Port 3 - frame sync trans-<br>mit         |  |

| 74B | GND          | -   | -               | Ground                                                                 |  |

| 75B | N/C          | -   | -               | No connect                                                             |  |

| 76B | JTAG_EMU1    | IO  | VDDSHV          | JTAG - test emulation                                                  |  |

| 77B | xJTAG_RTCK   | 0   | VDDSHV          | JTAG - test clock - ARM clock emulation                                |  |

| Pin | Signal   | I/O | Signal<br>Level | Description             |

|-----|----------|-----|-----------------|-------------------------|

| 78B | JTAG_TCK | I   | VDDSHV          | JTAG - test clock       |

| 79B | GND      | -   | -               | Ground                  |

| 80B | JTAG_TMS | IO  | VDDSHV          | JTAG - test mode select |

#### Table 2-2. Pin Descriptions, phyCORE-Connector X2, Row B (Continued)

#### Table 2-3. Pin Descriptions, phyCORE-Connector X2, Row C

| Pin | Signal        | I/O     | Signal<br>Level | Description                                                                                                                                                                            |

|-----|---------------|---------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1C  | VIN           | Ι       | VIN             | 3.3V-5.0 power input                                                                                                                                                                   |

| 2C  | VIN           | I       | VIN             | 3.3V-5.0 power input                                                                                                                                                                   |

| 3C  | GND           | -       | -               | Ground                                                                                                                                                                                 |

| 4C  | VIN_3V3       | I       | VIN_3V3         | 3.3V power input                                                                                                                                                                       |

| 5C  | VIN_3V3       | I       | VIN_3V3         | 3.3V power input                                                                                                                                                                       |

| 6C  | VBAT          | I       | Power           | Battery connection to PMIC switch supplying power to the VRTC                                                                                                                          |

| 7C  | GND           | -       | -               | Ground                                                                                                                                                                                 |

| 8C  | /RESET        | OD      | VIN             | Active low reset out (open drain), normally connected to<br>other open drain reset control inputs; this signal indi-<br>cates all power supplies on the SOM are within regula-<br>tion |

| 9C  | xSYS_NRESWARM | IO<br>D | VDDSHV          | Active low processor warm reset (input / open drain out-<br>put)                                                                                                                       |

| 10C | xSYS_CLKOUT1  | 0       | VDDSHV          | System clock out 1                                                                                                                                                                     |

| 11C | SYS_BOOT6     | I       | VDDSHV          | Boot configuration (sampled at reset)                                                                                                                                                  |

| 12C | GND           | -       | -               | Ground                                                                                                                                                                                 |

| 13C | SYS_BOOT4     | Ι       | VDDSHV          | Boot configuration (sampled at reset)                                                                                                                                                  |

| 14C | SYS_BOOT3     | Ι       | VDDSHV          | Boot configuration (sampled at reset)                                                                                                                                                  |

| 15C | UART1_RX      | I       | VDDSHV          | UART 1 receive data into SOM                                                                                                                                                           |

| 16C | UART1_TX      | 0       | VDDSHV          | UART 1 transmit data from SOM                                                                                                                                                          |

| 17C | GND           | -       | -               | Ground                                                                                                                                                                                 |

| 18C | ENET_TXP      | 0       | Analog          | Ethernet Differential (transmit positive)                                                                                                                                              |

| 19C | ENET_TXN      | 0       | Analog          | Ethernet Differential (transmit negative)                                                                                                                                              |

| 20C | ENET_RXP      | Ι       | Analog          | Ethernet Differential (receive positive)                                                                                                                                               |

| 21C | ENET_RXN      | I       | Analog          | Ethernet Differential (receive negative)                                                                                                                                               |

| 22C | GND           | -       | -               | Ground                                                                                                                                                                                 |

| 23C | MMC1_DAT7     | Ю       | VDDSHV          | MMC / SDIO 1 interface - data                                                                                                                                                          |

| 24C | MMC1_DAT6     | Ю       | VDDSHV          | MMC / SDIO 1 interface - data                                                                                                                                                          |

| 25C | MMC1_DAT4     | Ю       | VDDSHV          | MMC / SDIO 1 interface - data                                                                                                                                                          |

| 26C | MMC1_DAT3     | 10      | VDDSHV          | MMC / SDIO 1 interface - data                                                                                                                                                          |

### Table 2-3. Pin Descriptions, phyCORE-Connector X2, Row C (Continued)

| Pin | Signal         | I/O | Signal<br>Level     | Description                                                                    |  |

|-----|----------------|-----|---------------------|--------------------------------------------------------------------------------|--|

| 27C | GND            | -   | -                   | Ground                                                                         |  |

| 28C | xMCSPI1_CLK    | 10  | VDDSHV              | Multichannel Buffered Serial Port 1 - clock                                    |  |

| 29C | MCSPI1_SOMI    | 10  | VDDSHV              | Multichannel Serial Peripheral Interface 1 - Slave data<br>out, Master data in |  |

| 30C | MCSPI1_CS3     | 0   | VDDSHV              | Multichannel Serial Peripheral Interface 1 - chip select 0                     |  |

| 31C | MCSPI1_CS2     | 0   | VDDSHV              | / Multichannel Serial Peripheral Interface 1 - chip select                     |  |

| 32C | GND            | -   | -                   | Ground                                                                         |  |

| 33C | MCBSP2_DX      | 10  | VDDSHV              | Multichannel Buffered Serial Port 2 - data transmit                            |  |

| 34C | MCBSP2_DR      | I   | VDDSHV              | Multichannel Buffered Serial Port 2 - data receive                             |  |

| 35C | MCBSP2_CLKX    | 10  | VDDSHV              | Multichannel Buffered Serial Port 2 - TX clock                                 |  |

| 36C | MCBSP1_FSR     | 10  | VDDSHV              | Multichannel Buffered Serial Port 1 - frame sync receive                       |  |

| 37C | GND            | -   | -                   | Ground                                                                         |  |

| 38C | MCBSP1_CLKR    | 10  | VDDSHV              | Multichannel Buffered Serial Port 1 - RX clock                                 |  |

| 39C | MCBSP_CLKS     | 10  | VDDSHV              | Multichannel Buffered Serial Port - clock                                      |  |

| 40C | UART3_TX_RS232 | 0   | RS232/              | UART 3 transmit at RS-232 levels                                               |  |

|     |                |     | VDDSHV <sup>a</sup> |                                                                                |  |

| 41C | UART3_RX_RS232 | Ι   | RS232/              | UART 3 receive at RS-232 levels                                                |  |

|     |                |     | VDDSHV <sup>a</sup> |                                                                                |  |

| 42C | GND            | -   | -                   | Ground                                                                         |  |

| 43C | UART2_CTS      | I   | VDDSHV              | UART 2 clear to send                                                           |  |