Phytec中国的wiki

support@phytec.cn![]()

热线:0755-61802110-803

Page History

...

| 信号 | 解释 |

|---|---|

| D[31:0] | 数据 |

| AD[15:0] | 地址/数据复用 |

| ADDR[25:16] | 地址 |

| CS#[5:0] | 片选 |

| EB#[3:0] | 32个字节,每个字节的使能输出引脚 |

| OE | 当这个输出信号拉低时,外部器件可以在总线上输出信号 |

| RW | 指示目前是写还是读 |

| BCLK | 同步模式:时钟 |

| LBA | 同步burst模式:让外部器件载入一个新的地址 |

| WAIT/DTACK_B | 异步模式(DTACK):等待外部器件直到数据可用 同步burst模式(WAIT):外部器件准备好传输数据 |

| CRE | 用于CellularRam |

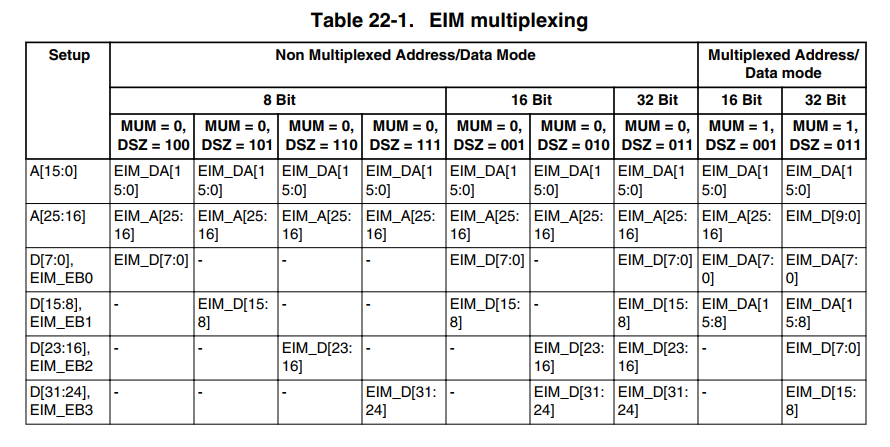

各个模式下的引脚分配

由于某些引脚未引出,核心板能做到EIM由于某些引脚未引出,phyCORE i.MX6核心板能做到EIM_D[15:0],EIM_DA[15:0],EIM_A[25:16]。

控制信号中,EIM_WAIT未引出。

如果要使用未引出的引脚,请考虑使用phyFlex 如果要使用未引出的引脚,请考虑使用phyFLEX i.MX6核心板。

| Table Filter | ||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||

|

...

Overview

Content Tools

Tasks